**Energy Efficient Innovations**

# **IGBT** Applications Handbook

Copyright © 2014, SCILLC

THIS PAGE INTERNIONALIN LETTERANK

# **IGBT Applications**

Handbook

HBD871/D Rev. 3, Apr-2014

© SCILLC, 2014 Previous Edition, 2012 "All Rights Reserved"

Grafoil is a registered Union Carbide. Kon–Dux and Rubber–Duc are trademarks of Aavid Thermal Technologies, Inc. Thermasil is a registered trademark and Thermafilm is a trademark of Thermalloy, Inc. Kapton is a registered trademark of du Pont de Nemours & Co., Inc. Sil–Pad is a registered trademark of the Bergquist Company. CHO–THERM is a registered trademark of Chomerics, Inc. FULLPAK, ICePAK and Thermopad are trademarks of Semiconductor Componenets Industries, LLC.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILL's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ScILL reserves the right to make changes without further notice to any products herein. SCILL makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subdiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attromy fees arising out of, directly or indirectly, or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or mautacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This lite

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA **Phone**: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada **Email**: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada. Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

www.onsemi.com

**IGBT** Applications Handbook

# **Table of Contents**

| Introduction. |  |  |  |  |  |  |  |  |  |  |  |  |  |  | 5 |  |

|---------------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|---|--|

|               |  |  |  |  |  |  |  |  |  |  |  |  |  |  |   |  |

#### **Device Data**

| Device Physics of the IGBT (AND9070/D)        | 6  |

|-----------------------------------------------|----|

| Reliability and Quality for IGBTs (AND9058/D) | 11 |

| Reading IGBT Data Sheets (AND9068/D)          | 17 |

#### **Electrical Design**

| How to Use Thermal Data Found in Data Sheets<br>(AND8220/D) | 26 |

|-------------------------------------------------------------|----|

| IGBT Gate Drive (AND9052/D)                                 |    |

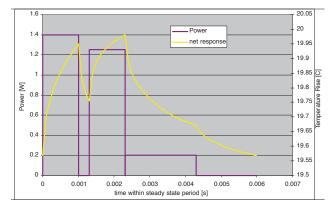

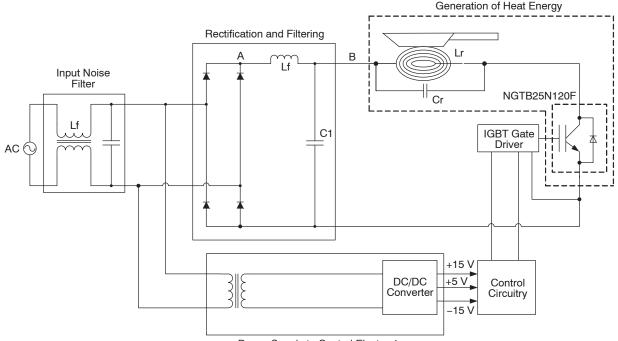

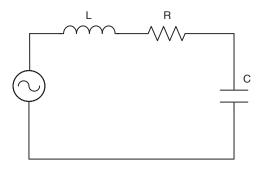

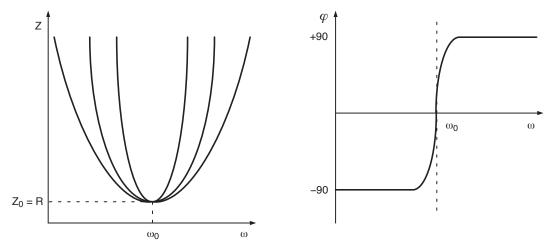

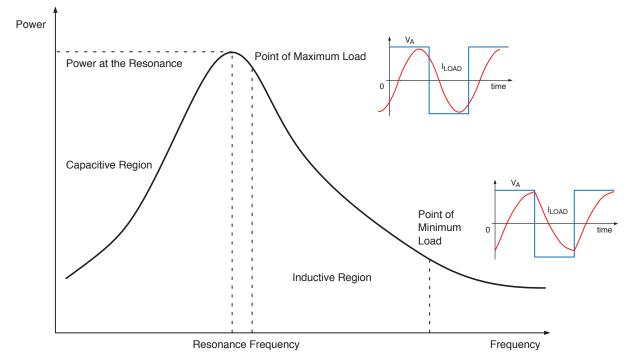

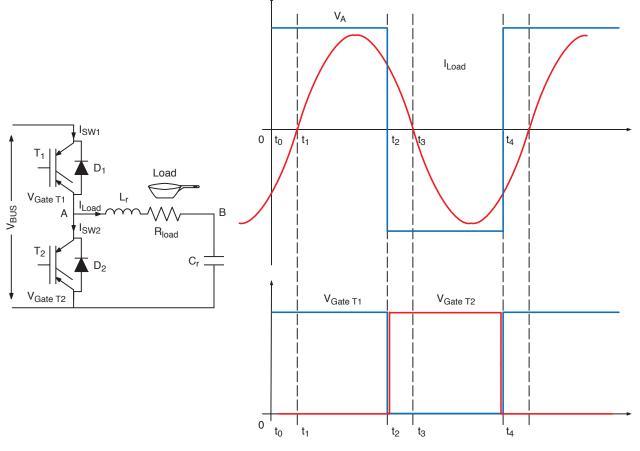

| Inductive Heating Power Losses (AND9054/D)                  | 48 |

| IGBTs for Inductive Heating Applications (AND9056/D)        | 53 |

| ESD and IGBTs (AND9059/D)                                   | 57 |

| Noise Management for IGBTs (AND9071/D)                      | 60 |

| Gate Emitter Voltage vs. Losses (AND9072/D)                                    | 67         |

|--------------------------------------------------------------------------------|------------|

| ON Semiconductor's Motor Control IGBTs and Free-Wheeling<br>Diodes (AND9088/D) | 71         |

| Paralleling of IGBTs (AND9100/D)                                               | 91         |

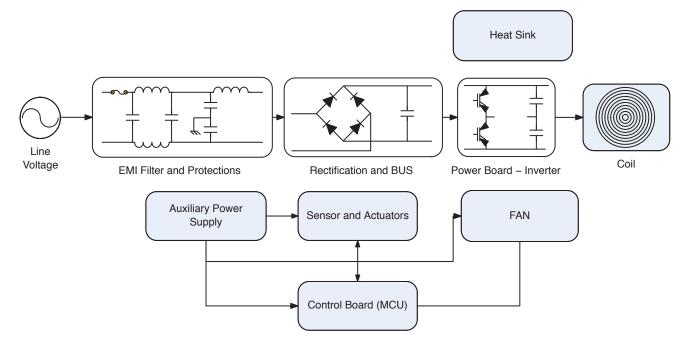

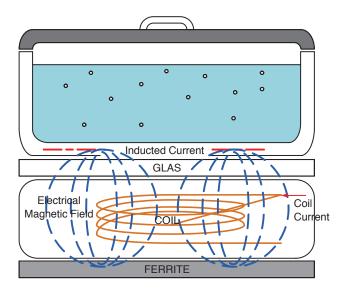

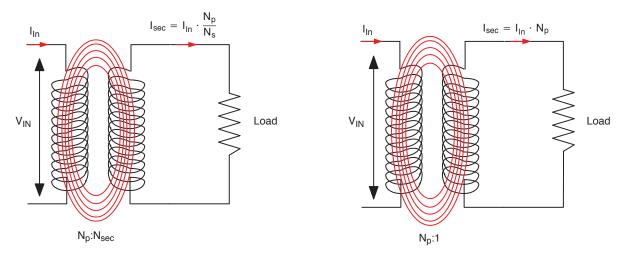

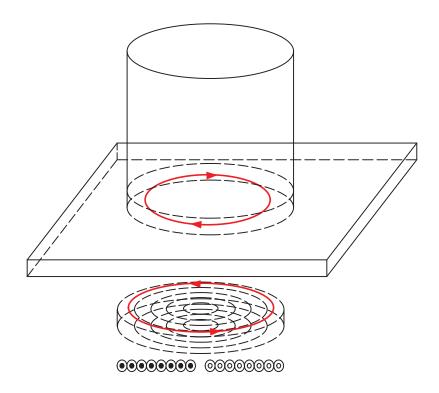

| Induction Cooking (AND9166/D)                                                  | <b>9</b> 8 |

#### Thermal/Mechanical

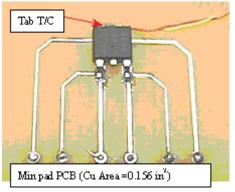

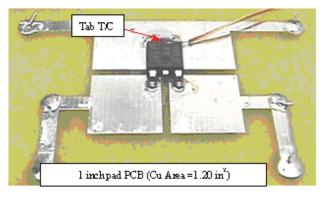

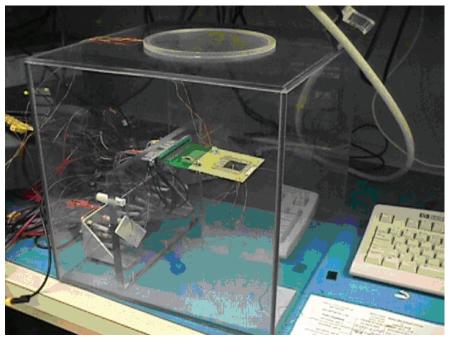

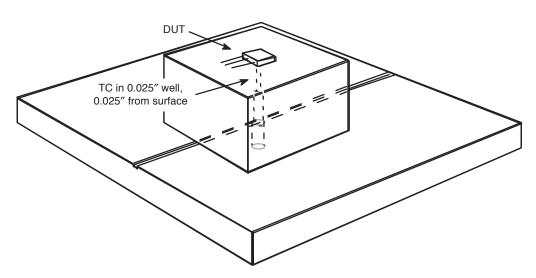

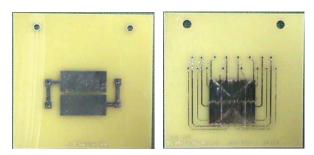

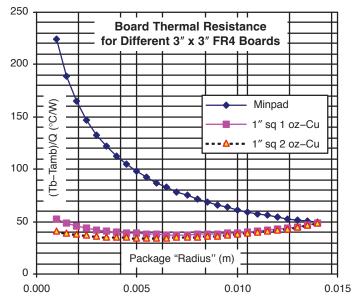

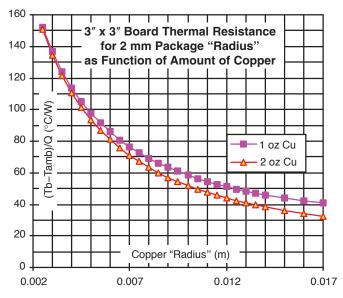

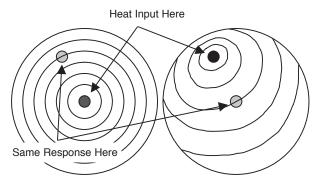

| Semiconductor Package Thermal Characterization<br>(AND8215/D)                                       | 120 |

|-----------------------------------------------------------------------------------------------------|-----|

| Predicting the Effect of Circuit Boards on Semiconductor<br>Package Thermal Performance (AND8222/D) | 134 |

| Thermal Calculations for IGBTs (AND9140/D)                                                          | 149 |

| Sales and Design Assistance                                                                         | 156 |

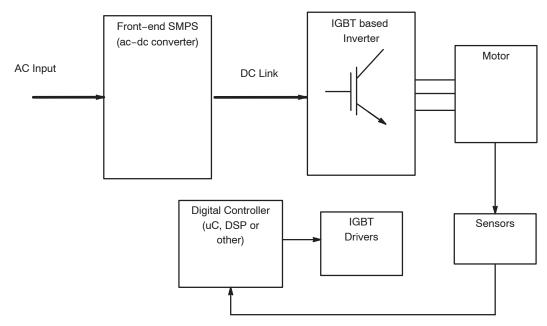

# Introduction

The IGBT is a four layer, semiconductor device that combines the voltage characteristics of a bipolar transistor (collector – emitter) and the drive characteristics of a MOSFET. The concept was first documented in a Japanese patent by Yamagami, which was filed in 1968. The first devices were of a planar technology, but more recently vertical, trench devices have been made popular.

The popularity of the IGBT has soared in recent years due to an increase in high voltage, high power applications at which they excel. While the switching speeds are slower than a MOSFET, the  $V_{CE(SAT)}$  characteristics are a significant improvement over those of a MOSFET at high currents, especially for high voltage devices. They are available in a range of voltage ratings from 300 to over 1200 volts and current ratings of 15 to 100 amps for a single die. IGBT modules have current ratings well into the 100s of amps.

The range of ratings of an IGBT make it well suited for high power applications such as:

- Electric vehicle motor drives

- Appliance motor drives

- Power factor correction converters

- Solar inverters

- Uninterruptable power supplies (UPS)

- Inductive heating cookers

- High frequency welders

This manual contains a collection of application notes that are available to help designers with the thermal, mechanical and electrical challenges of an IGBT based power converter. In addition, ON Semiconductor has a staff of skilled marketing and application engineers to assist customers with specific needs.

# AND9070/D

# **Device Physics of the IGBT**

#### **ON Semiconductor®**

http://onsemi.com

#### **APPLICATION NOTE**

#### INTRODUCTION

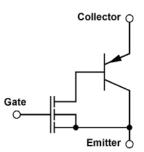

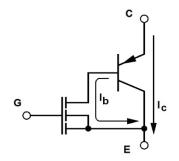

The Insulated Gate Bipolar Transistor (IGBT) evolved from the vertical power MOSFET in the mid 1980's. The simple addition of an extra P-N junction to the drain of the MOSFET changes this unipolar device into a Bipolar Junction Transistor. However, because of the MOS gate structure, this BJT is a voltage controlled device.

This combination of an insulated gate input and bipolar output makes the IGBT an excellent power switch for medium frequency (5 - 50 kHz) and high voltage (200-2000 V) applications. 600 V and 1200 V are the most widely used voltage platforms for white goods and industrial motor drive applications. Improvements in device design and semiconductor processing continue to increase the IGBT's frequency and reduce its conduction voltage drop, while maintaining high blocking voltage capability. The current carrying capability is only limited by the paralleling of large area IGBT's in multiple die modules.

The following sections discuss the design and operation of discrete vertical power IGBT's as large signal switches. This applications note emphasizes the blocking, conduction, and switching of the IGBT for high performance power conversion. Lastly, The Safe Operating Area and temperature effects of the IGBT will be examined.

#### **DEVICE STRUCTURE**

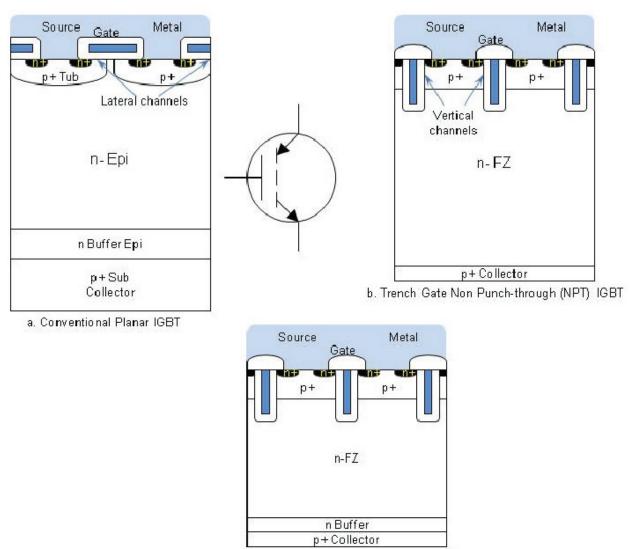

Vertical cross-sections of a planar n-channel IGBT are shown in Figure 1. Complementary P-channel IGBT's also exist, but have higher on-state losses and latch-up more easily than N-channel IGBT's. These cross-sections show a single IGBT cell, typically 2 to 10  $\mu$ m wide, where the products are designed by integrating several million cells in a single silicon chip to provide 10's and 100's of amperes of current depending on the voltage rating.

Many features of IGBTs are adapted from power MOSFETs with high cell densities on the semiconductor die to achieve the desired current rating. But due to the device concept of IGBT with conductivity of modulation it can handle a much higher current density compared to a MOSFET. The high current density enabled by an IGBT allows 3X die size reduction for 600 V, and the advantage for the IGBT increases further as the voltage increases.

Not shown in Figure 1 are the high voltage termination and bonding areas for electrically and thermally connecting

the IGBT to a three-terminal package. Termination is typically implemented by a number of P-type rings and field plates which are carefully designed and tailored in order to achieve the desired high voltage.

Figure 1a shows a representative cross section of conventional planar IGBT and its equivalent circuit. In this structure the silicon surface is planar and the channel regions which are created and controlled by the gate bias, form a lateral current path for conduction from the bottom p+ collector to the surface N+ emitter region. The channel is formed by applying positive gate-to-emitter voltage which inverts the surfaces of the P+ tubs from P-type to N-type, thereby creating conduction path for electrons from the n+ emitter, through the channel to the N-type epi.

A drawback for planar IGBTs is that current flow is constricted between the p+ tubs in what is known as the JFET region. Even though techniques are used to increase carrier concentration in the JFET, this region continues to pose a limitation to planar gated devices. The channel operation of an IGBT is the same as the MOSFET conduction, but since an IGBT has a P+ backside collector, the channel current serves as the base current to activate a PNP bipolar transistor. Since а BJT is a conductivity-modulated device the voltage drop (V<sub>CEsat</sub>) in the IGBT is significantly reduced. Thus the secret of an efficient IGBT is combining the voltage controlled MOS gate with high input resistance, and a low V<sub>CEsat</sub> bipolar transistor.

As seen in the vertical cross section, the IGBT is composed of a four layer NPNP semiconductor. It is very important to suppress this parasitic NPNP thyristor device by controlling the gains of the interlocked BJTs forming the thyristor. The parasitic NPN transistor is designed to be inactive, as its emitter-base junction is shorted out by the MOSFET source metal. Therefore the basic IGBT is a vertical wide-base PNP transistor, with its base drive provided by the surface MOSFET. The simple four layer device of Figure 1a has several drawbacks affecting switching and SOA.

To overcome these limitations several techniques are devised in modern IGBTs to modify the vertical structures as IGBT design has progressed over the past three decades. The Punch-Through (PT) IGBT, shown in Figure 1a, implemented by epitaxy, has been predominantly used in lower voltages below 600V for good breakdown voltage and low V<sub>CEsat</sub>. A PT-IGBT has an extra N+ region (buffer layer) epitaxially grown on the thick P+ substrate prior to the N- epitaxy. During the off-state, the blocking voltage (BVces) completely depletes the Nregion, "punching-thru" to the N+ layer. The additional N+ buffer layer prevents "reach-thru" (voltage collapse from collector to emitter) to the P+ substrate, but allows a relatively thin Nregion which minimizes  $V_{CE(on)}$  while maximizing  $V_{(BR)CES}$ . The N+ region also improves the switching speed of the IGBT by reducing excess hole injection from the P+ substrate. The PT-IGBT also has a heavy P+ tub in the emitter region, which improves the  $V_{\text{BE}}$  shorting of the parasitic NPN, for improved SOA.

PT-IGBT's are typically available in 300 volt to 1200 V  $V_{(BR)CES}$  rated devices. Nonetheless, planar IGBTs based on PT epitaxy have disadvantages. It is expensive and difficult to grow defect free epitaxy more than 100 µm thick which is required for IGBTs of 1200 V and above. More seriously epi is grown on heavily doped substrates to reduce  $V_{CEsat}$ , but the high doping level injects large concentrations of minority carriers (PNP holes) which take considerable time to be removed during IGBT turn off. As a result, large switching losses occur, limiting the high frequency operation of these IGBTs to only few kHz.

To circumvent this problem, a Non-Punch-Thru (NPT) IGBT as shown in Figure 1b is utilized. NPT-IGBT's have a thicker N- region which is fabricated using N- Float Zone wafers and is wide enough to prevent high voltage punch-thru. A shallow P+ collector is implanted on the backside of the wafer. Precise control of this P+ implant dose and junction depth results in reduced PNP hole injection compared to the PT-IGBT. This precise hole distribution results in a fast switching NPT-IGBT without having to use the lifetime killing processes common in PT-IGBT's. With this improvement in technology, the Float Zone wafer can be thinned to less than 100 µm and back phosphorus implantation is used to form the N+ region to block the electrical field reaching the P+ collector under the high voltage condition resulting in the field stop IGBT, which improves the DC and switching performance. In Figure 1a, the IGBT has a planar-gate structure.

The performance of IGBTs has been improved significantly by using a trench-gate structure similar to that used in trench MOSFETs. Trench gates provide higher channel density (small cell size) and reduce the JFET resistance in the IGBT structure. In conventional planar IGBTs, current crowding and electric field curvature in the small space between p+ tubs does not allow for sufficient conductivity modulation. This effect is alleviated in trench IGBTs due the long distance between p+ tubs. The free carrier concentration in the N-drift region near the emitter is also enhanced, leading to a lower  $V_{CEsat}$ . Trench structure also provides a more robust IGBT as it more effectively

suppresses the latch-up of the NPNP four layer device. This is due to the fact that the n+ emitter (similar to the MOSFET source) can be made narrower and the p+ body can be more heavily doped. Suppression of NPNP latch-up and control of IGBT saturation current are used in IGBTs to provide products with excellent short circuit withstand capability and robust FBSOA.

In addition to trench gate and engineered cell architecture, advanced IGBTs are dramatically more enhanced by the field stop which is similar to the buffer layer concept presented earlier, but implemented in thin Float Zone substrates, as shown in Fig 1c. Using a thin wafer for a non-punch-through (NPT) IGBT and adding a field stop region enables several improvements. The term field refers to stopping the electric field by the n buffer layer, allowing a thinner wafer to be used for the same high breakdown voltage. Also, controlling the carrier concentration of both the field stop and p+ collector layers, controls the emitter efficiency of the backside junction. Thus, field stop technology provides faster switching and lower  $V_{CEsat}$  due to a thinner wafer, and adjustment of these parameters by carrier concentration control.

Freewheeling diodes are co-packaged with IGBTs in inductive load topologies. These high voltage IBGTs are designed with fast switching, low charge and soft recovery characteristics. Recent developments have been successful in the monolithic integration of rectifiers with IGBTs, allowing reverse conduction and much more efficient utilization of silicon real estate. This combination of the IGBT & diode has been enabled by modern field stop techniques. ON Semiconductor products employ the most advanced and proprietary techniques of field stop trench IGBTs providing compelling solutions to a variety of high performance power conversion applications, such as motor drive, renewable energy and white goods applications.

A few final comments comparing these structures follow. The basic IGBT and NPT-IGBT are nearly symmetrical blocking devices with V(BR)CES V(BR)ECS. However, the reverse leakage IECS is relatively high (mA range), as the backside P-N junction is sawn through and un-passivated. The PT-IGBT on the other hand is an asymmetric blocking device with V(BR)ECS << V(BR)CES due to the presence of the N+ buffer layer. But like the others, it also has a leaky IECS. Thus, third quadrant operation of most IGBT's is limited to low reverse voltage.

#### **OFF\_STATE CHARACTERISTICS**

For normal first quadrant operation of a low-side N-channel IGBT, the emitter is grounded, the collector is connected to  $+V_{CC}$  through some impedance and the gate  $V_{GE}$  controls the collector current. IGBT's are enhancement mode devices, that is, they are normally off for VGE < Vth  $\approx$  5 V. For V<sub>GE</sub> = 0 V, only a small (nA level) leakage current I<sub>CES</sub> flows through the collector-emitter terminals until VCE reaches the avalanche voltage V(BR)CES. The upper P-tub/N- junction supports this forward blocking voltage.

Usually the N- region's thickness and resistivity determine the V(BR)CES breakdown voltage. However, as discussed in the next section, the on-state VCE(off) also increases with N-thickness, so IGBT's are designed for the minimum Nthickness necessary for the V(BR)CES rating. For the 1200 V NPT-IGBT, this results in a wafer thickness of about 0.007 inch.

Besides the N- region, the device designer must consider several other factors that can affect V(BR)CES. These include the MOSFET polysilicon gate width (voltage breakdown between the cells), MOSFET P-tub width, depth, and concentration (curvature and punch-thru effects), and the high voltage planar edge termination and passivation. The termination design and passivation process are critical to the long term reliability of any high voltage semiconductor. Likewise for trench IGBTs, trench depth, trench spacing and p+tub concentration are critical for optimized breakdown voltage, along with optimized termination design.

#### **ON-STATE CHARACTERISTICS**

When  $V_{GE} > V_{th}$ , the MOSFET channel is inverted and electrons can flow from the N+ source (IGBT emitter) to the N- drain region, if VCE > 0.8 V. This VCE(offset) 0.8 V must be exceeded to forward bias the backside P-N junction and permit conduction. The MOSFET current ID = IB, the base current of the vertical PNP. For large VCE, the collector current of the IGBT saturates due to the transconductance of the MOSFET (g<sub>m</sub>) and the current gain of the PNP (beta) according to the equation:

$$I_{C(sat)} = g_m(\beta + 1) (V_{GE} - V_{th})^2$$

Like any MOSFET, <sup>g</sup>m is a function of the gate oxide capacitance, electron mobility, and the channel width/length ratio. Being a wide base BJT, the beta of the PNP is strongly dependant on the N- region minority carrier lifetime, the N+ buffer layer profile (for a PT-IGBT), and the backside P+ doping profile (which internally is the emitter of the PNP). Carrier lifetime is customarily reduced during manufacturing to improve the switching speed of the IGBT. This lowers the PNP beta, and increases the linear region VCE(on).

For hard switching applications, the linear region VCE(on) is a critical parameter to enable fast switching, as it determines the on-state power dissipation, and is a direct trade-off with the switching losses mentioned above. The VCE(on) in the linear region has three components:

$$V_{CE(on)} = V_{CE(offset)} + V_{(N-region)} + V_{DS(surface MOSFET)}$$

Provided that a good ohmic contact exists to the collector P+, the slope of the VCE(on) linear region is controlled primarily by the latter two terms. The resistance of the N-region is conductivity modulated by the bipolar action (electron and hole conduction) of the IGBT. This increased conductivity results in significantly lower VCE(on) at a given current density compared to the unipolar MOSFET of equal voltage rating. At IC = 100 A/cm2, (typically 20 A in

a TO-220 package), a fast IGBT's VCE(on) is roughly one third the VDS(on) of a MOSFET at ID = 100 A/cm2.

Such improvement in on-state voltage drop is not without consequence. The excess hole carriers in the N- region must be injected and removed during turn-on and turn-off, respectively. Thus the IGBT has slower switching capability than the MOSFET, as discussed in the next section. The IGBT switching speed/VCE(on) trade-off can be tailored for the operating frequency to minimize total system dissipation. For PT-IGBT's this is usually done by adjusting the final carrier lifetime. For NPT-IGBT's, the backside P+ profile is adjusted to control the excess hole distribution, so that carrier lifetime killing is usually not required. Using these methods, switching fall times of 100 to 300 nsec can be achieved. Lastly, the third term (VDS), like gm, is primarily determined by the packing density of the MOSFET cells. A high channel width/length ratio reduces total channel resistance. Also the drain region under the gate is not highly conductivity modulated, especially for planar IGBT, so that the polysilicon gate width must be optimized for VCE(on) as well as V(BR)CES.

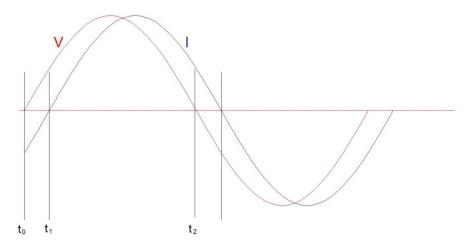

#### SWITCHING CHARACTERISTICS

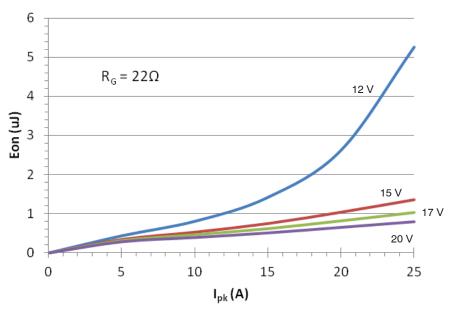

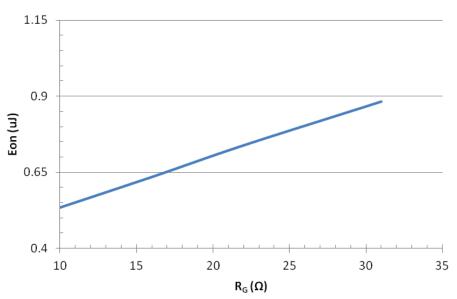

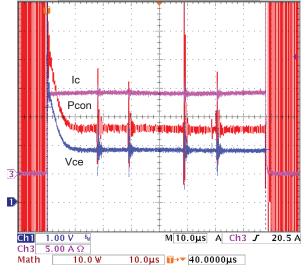

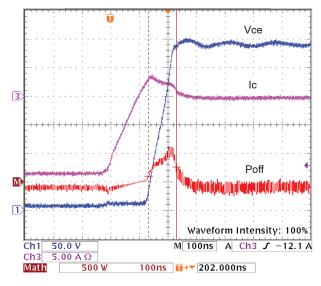

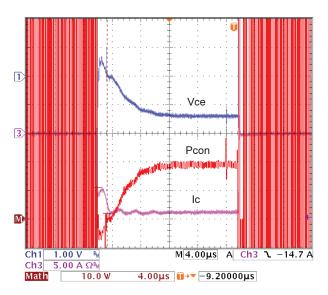

IGBT's are often used in PWM inverters with freewheeling diodes commutating the load current between the power switches. The turn-on switching loss (Eon) is dominated by the voltage fall time  $(t_{fv})$  of the V<sub>CE</sub> waveform, which exponentially falls to the on-state  $V_{CE(on)}$ . The t<sub>fv</sub> exponential time constant is proportional to the minority carrier lifetime and beta of the PNP. The lifetime can be reduced by heavy metal doping or by high energy particle bombardment creating recombination centers in the silicon lattice. The PNP beta can be reduced by increasing the N+ buffer concentration (PT-IGBT) or decreasing the P+ backside effective emitter doping (NPT-IGBT). Use of both lifetime killing and beta reduction, or other novel recombination structures now in development, are expected to push IGBT fall times to the 50 nsec range.

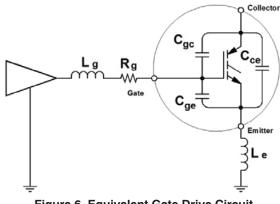

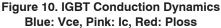

Gate capacitance and gate charge play an important role in turn-on switching characteristics. It is critical to reduce input capacitance and charge to minimize delay times, rise times and drive current for IGBT turn on. In addition, the capacitance and gate charge associated with gate-to-collector (or Miller) capacitance is not only very influential in dynamic performance of MOS-gated devices, but to device robustness and operation stability. The turn-off switching loss (E<sub>OFF</sub>) is dominated similarly by the IGBT's current fall time (t<sub>fi</sub>), which is also proportional to the carrier lifetime and PNP beta. As lifetime and beta are reduced to improve switching losses, the on-state V<sub>CE(on)</sub> increases due to the reduced conductivity of the N region. As mentioned before, the device designer must optimize the IGBT's speed/V<sub>CE(on)</sub> trade-off for the operating frequency of the application. During switching, or during fault

conditions, high IC and  $V_{CE}$  are present simultaneously, which leads to the next topic.

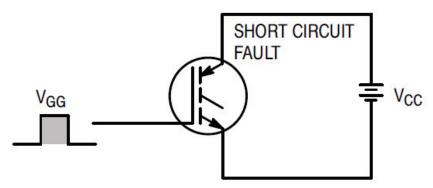

SOA. The Safe Operating Area (SOA) is defined as the loci of points where the load line (V<sub>CE</sub> and I<sub>C</sub>) may safely traverse the output characteristics of a device at a specified junction temperature and pulse width. BJT's specify two types of SOA: Forward Biased (FBSOA) and Reverse Biased (RBSOA). Since the IGBT base region is floating and cannot be reversed biased, and since the PNP beta is normally so low that PNP  $BV_{CEO} \approx BV_{CES}$ , the IGBT's FBSOA and RBSOA are similar, although RBSOA is slightly less as explained below. IGBT SOA capability is a function of many device design parameters, including lifetime, beta, P-tub doping profile, and MOSFET cell geometry. SOA failures can occur via two distinct mechanisms. The first mechanism is a current induced failure, due to excessive hole carriers in the P-tub region, which internally biases the parasitic NPN, causing latch-up of the parasitic four layer NPNP thyristor. FBSOA is normally a current induced failure. The second mechanism is an electric field induced failure, due to the excessive charge distribution narrowing the depletion region in the Nregion, which causes avalanche injection and voltage collapse.

During RBSOA, the electron (MOSFET) current turns off first, leaving an excess of holes in the N- region. These holes add to the donor charge, effectively reducing the Nresistivity and breakdown voltage. RBSOA is normally an electric field induced failure. Both FBSOA and RBSOA are affected by the junction temperature.

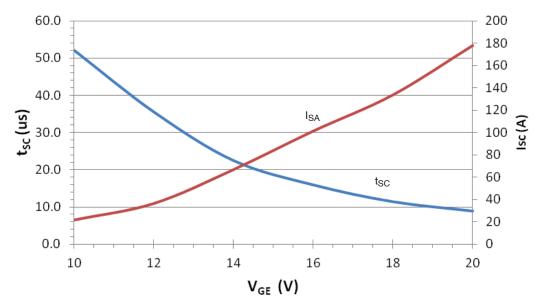

A third SOA rating for IGBTs is Short Circuit (SCSOA). During fault conditions such as a shorted load, the IGBT must survive until the protection circuitry detects the fault and shuts down the system. The device must be designed to survive three modes of SCSOA; turning on into the short (mode A), surviving the high  $I_C$  and  $V_{CE}$  conduction period (mode B), and then turning off safely (mode C). The failure mechanism in each mode is as follows:

- Failure Mode A is FBSOA latchup induced.

- Failure Mode B is simply power dissipation limited.

- Failure Mode C is RBSOA avalanche induced.

The standard specification for SCSOA is surviving for 10  $\mu$  sec at a starting  $T_J = 150^{\circ}$ C, non-repetitively (since  $T_J$  will exceed 150°C). Special IGBT cell design featuring hole-bypass or ballast structures is necessary to survive these severe SCSOA conditions. The fourth and final SOA condition is Unclamped Inductive Switching (UIS). IGBT's are much weaker in UIS than power MOSFETs, due to the hole current present in the IGBT. Because of this, IGBT's are usually clamped well below  $V_{(BR)CES}$ , but high dv/dt excursions can cause momentary spikes and UIS failure. One solution to this problem is to add series Rg to the gate drive circuit, limiting the dv/dt. "Smart" IGBT's are also becoming commercially available with current limiting and temperature sensing, providing SOA protection on chip.

#### **TEMPERATURE CHARACTERISTICS**

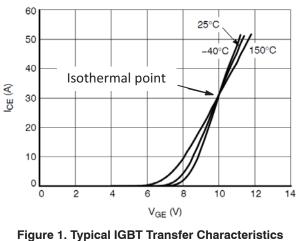

IGBT's with a maximum junction temperature rating of 150°C are typically operated with an average  $T_J$  of 75 to 125°C. Therefore the temperature dependence of the on-state and switching characteristics is of primary concern in system design. For this discussion, it is assumed that the device designer has optimized the IGBT for safe operation up to 150°C within the SOA ratings. It remains to describe the effect of temperature on  $V_{CE(on)}$ ,  $E_{ON}$ , and  $E_{OFF}$ .

As discussed before, the  $V_{CE(on)}$  is composed of the  $V_{CE(offset)}$ , the V(N- region), and the  $V_{DS(MOSFET)}$ . These three components are affected by several semiconductor parameters that are temperature dependent.

#### PARAMETER TEMP EFFECT (75°C to 125°C)

- intrinsic carrier concentration increases

- minority carrier lifetime increases

- carrier mobility decreases

$V_{CE(OFFSET)}$  decreases as the intrinsic carrier concentration increases. V(N-region) varies in a complex way, because the lifetime increase lowers V(N-), while the mobility decrease with a raise in V(N-). For PT-IGBT's with lifetime killing, the lifetime effect dominates and V(N-) decreases with T<sub>J</sub>. For NPT-IGBT's without lifetime killing, the mobility effect dominates and V(N-) increases with T<sub>J</sub>. V<sub>DS(MOSFET)</sub> also varies in a complex way as V<sub>th</sub> is also temperature dependent.

For most applications  $V_{GE} >> V_{th}$  (high I<sub>C</sub>), so then  $V_{DS}$  is dominated by the decrease in mobility and  $V_{DS}$  increases with T<sub>J</sub>. The combined temperature effect of these three components is as follows. The  $V_{CE(on)}$  of PT-IGBT's has a slightly negative temperature coefficient. The  $V_{CE(on)}$  of NPT-IGBT's has a slightly positive temperature coefficient. This makes the NPT-IGBT the better choice when paralleling IGBT's, as their positive temperature coefficient improves current sharing.

Both  $E_{on}$  and  $E_{off}$  increase with temperature, as the lifetime increase causes the IGBT fall time to increase, due to both slower carrier recombination and higher PNP beta. The NPT-IGBT fall time has a higher thermal coefficient than the PT-IGBT, as the beta increase causes excess carriers which cannot easily recombine in the higher lifetime NPT-IGBTs.

#### CONCLUSION

The IGBT has become the power switch of choice in medium and high power applications. The combination of speed, on-voltage, wide SOA, ease of drive, and relatively small temperature coefficients give the IGBT significant advantages over MOSFET's and BJT's. The growth of IGBTs is rapidly expanding due the massive adoption of variable speed (frequency) motor drives, white goods energy efficiency, the proliferation of renewable inverter applications and advent of electric vehicles.

### AND9070/D

c. Trench Gate Field Stop IGBT

Figure 1. Insulated Gate Bipolar Transistor (IGBT) Structures

# **Reliability and Quality for IGBTs**

#### **ON Semiconductor®**

http://onsemi.com

#### **APPLICATION NOTE**

#### INTRODUCTION

In today's semiconductor marketplace two important elements for the success of a company are product quality and reliability. Both are interrelated – reliability is the quality extended over the expected life of the product. For any manufacturer to remain in business, their products must meet and/or exceed the basic quality and reliability standards. ON Semiconductor, as a semiconductor supplier, has successfully achieved these standards by supplying product for the most strenuous applications to perform in the most adverse environments.

It is recognized that the best way to accomplish an assured quality performance is by moving away from the previous methods of "testing in" quality and embracing the newer concept of "designing in" quality. At ON Semiconductor, we use a two-fold approach toward reaching the ultimately achievable level of quality and reliability. First, we develop and implement a process that is inherently reliable. Then we exercise meticulous care in adhering to the specifications of the process every step of the way – from start to finish. This allows the development and application of inspections and procedures that will uncover potentially hidden failure modes. It is this dedication to long–term reliability that will ultimately lead to the manufacture of the "perfect product."

ON Semiconductor approaches the ideal in IGBT product reliability by instigating a four-step program of quality and reliability:

- 1. Stringent in-process controls and inspections.

- 2. Thoroughly evaluated designs and materials.

- 3. Process average testing, including 100% QA redundant testing.

- 4. Ongoing reliability verifications through audits and reliability studies.

These quality and reliability procedures, coupled with rigorous incoming inspections and outgoing quality control inspections add up to a product with quality built in – from raw silicon to delivered service.

#### **RELIABILITY TESTS**

ON Semiconductor IGBT's are subjected to a series of extensive reliability tests to verify conformance. These tests are designed to accelerate the failure mechanisms encountered in practical applications, thereby ensuring satisfactory reliable performance in "real world" applications.

The following describes the reliability tests that are routinely performed on ON Semiconductor's IGBT's.

#### High Temperature Reverse Bias (HTRB):

The HTRB test is designed to check the stability of the device under "reverse bias" conditions of the main blocking junction at high temperature, as a function of time.

The stability and leakage current over a period of time, for a given temperature and voltage applied across the junction, is indicative of junction surface stability. It is therefore a good indicator of device quality and reliability.

For IGBT's, voltage is applied between the collector and emitter with the gate shorted to the emitter. I<sub>CES</sub>,  $V_{(BR)CES}$ , I<sub>GES</sub>,  $V_{GE(th)}$ , and  $V_{CE(on)}$  are the dc parameters monitored. A failure will occur when the leakage achieves such a high level that the power dissipation causes the devices to go into a thermal runaway. The leakage current of a stable device should remain relatively constant, only increasing slightly over the testing period.

Typical conditions:

$V_{CE} = 80\% - 100\%$  of maximum rating  $V_{GE} = 0$  V (shorted)  $T_A = 150$ C or Tj maximum Duration: 1000 hrs for qualification

#### High Temperature Gate Bias (HTGB):

The HTGB test is designed to electrically stress the gate oxide at the maximum rated dc bias voltage at high temperature. The test is designed to detect for drift caused by random oxide defects and ionic oxide contamination.

For IGBTs, voltage is applied between the gate and emitter with the collector shorted to the emitter.  $I_{GES}$ ,  $V_{GE(th)}$ , and  $V_{CE(on)}$  are the dc parameters monitored. Any oxide defects will lead to early device failures.

Typical conditions:

$V_{GE} = \pm 20$  V or 100% rated Vge  $V_{CE} = 0$  (shorted)

$T_J = 150^{\circ}C$  or  $T_J$  maximum Duration: 1000 hrs for qualification

#### High Temperature Storage Life (HTSL) Test:

The HTSL test is designed to indicate the stability of the devices, their potential to withstand high temperatures and the internal manufacturing integrity of the package. Although devices are not exposed to such extreme high temperatures in the field, the purpose of this test is to accelerate any failure mechanisms that could occur during long periods at storage temperatures.

The test is performed by placing the devices in a mesh basket, then placed in a high temperature chamber at a controlled ambient temperature, as a function of time.

Typical conditions:

$T_A = 150^{\circ}C$  on Plastic package Duration: 1000 hrs for qualification

# High Humidity High Temperature Reverse Bias (H<sup>3</sup>TRB)

The H<sup>3</sup>TRB test is designed to determine the resistance of component parts and constituent materials to the combined deteriorative effects of prolonged operation in a high temperature/high humidity environment. This test only applies to nonhermetic devices.

Humidity has been a traditional enemy of semiconductors, particularly plastic packaged devices. Most moisture related degradations result, directly or indirectly, from penetration of moisture vapor through passivating materials, and from surface corrosion. At ON Semiconductor, this former problem has been effectively addressed and controlled through use of junction "passivation" process, die coating, and proper selection of package materials.

Typical conditions:

$V_{CE} = 80\% - 100\% \text{ of maximum rating}$   $V_{GE} = 0 \text{ (shorted)}$   $T_A = 85^{\circ}C$  RH = 85%Duration: 1000 hrs for qualification Typical conditions:  $V_{GE} \ge 10 \text{ V}$

$V_{GE} \ge 10 \text{ V}$   $\Delta T_J = 100^{\circ}\text{C}$   $R_{\theta JC} = \text{Device dependent}$   $T_{on}, T_{off} \ge 30 \text{ seconds}$ Duration: 10 – 15k cycles for qualification

#### Unbiased Highly Accelerated Stress Test (UHAST)

The UHAST is designed to determine the moisture resistance of devices by subjecting them to high steam pressure levels. This test is only performed on plastic/epoxy encapsulated devices and not on hermetic packages (i.e., metal can devices). Within the chamber a tray is constructed inside to keep the devices approximately two inches above the surface of deionized water and to prevent condensed water from collecting on them. After achieving the proper temperature and atmospheric pressure, these test conditions are maintained for a minimum of 24 hours. The devices are then removed and air dried. Parameters that are usually monitored are leakage currents and voltage.

Typical conditions:  $T_A = 131^{\circ}C$  P = 14.7 psi RH = 100%Duration: 72 hrs for qualification

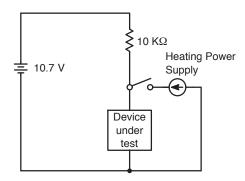

#### Intermittent Operating Life:

The purpose of the IOL test is to determine the integrity of the chip and/or package assembly by cycling on (device thermally heated due to power dissipation) and cycling off (device thermally cooling due to removal of power applied) as is normally experienced in a "real world" environment.

DC power is applied to the device until the desired function temperature is reached. The power is then switched off, and forced air cooling applied until the junction temperature decreases to ambient temperature.

$$\Delta T = \Delta T_{C} + R_{\theta JC} P_{D}$$

$$\Delta T_{J} = 100^{\circ} C$$

(typically, which is an accelerated condition)

$$\Delta T_{C} = T_{C HIGH} - T_{CLOW}$$

The sequence is repeated for the specified number of cycles. The temperature excursion is carefully maintained for repeatability of results.

The Intermittent Operating Life test indicates the degree of thermal fatigue of the die bond interface between the chip and the mounting surface and between the chip and the wire bond interface.

For IGBT's, parameters used to monitor performance are thermal resistance, threshold voltage, on-resistance, gate-emitter leakage current and collector-emitter leakage current.

A failure occurs when thermal fatigue causes the thermal resistance or the on-resistance to increase beyond the maximum value specified by the manufacturer's data sheets.

#### Temperature Cycle (TC):

The purpose of the Temperature Cycle Test is to determine the resistance of the device to high and low temperature excursions in an air medium and the effects of cycling at these extremes.

The test is performed by placing the devices alternatively in separate chambers set for high and low temperatures. The air temperature of each chamber is evenly maintained by means of circulation. The chambers have sufficient thermal capacity so that the specified ambient is reached after the devices have been transferred to the chamber.

Each cycle consists of an exposure to one extreme temperature for 15 minutes minimum, then immediately transferred to the other extreme temperature for 15 minutes minimum; this completes one cycle. Note that it is an immediate transfer between temperature extremes and thereby stressing the device greater than non-immediate transfer.

#### **Typical Extremes**

#### $-65/ + 150^{\circ}$ C

The number of cycles can be correlated to the severity of the expected environment. It is commonly accepted in the industry that ten cycles is sufficient to determine the quality of the device. Temperature cycling identifies any excessive strains set up between materials within the device due to differences in coefficients of expansion.

#### Low Temperature Storage Life (LTSL) Test:

The LTSL test is designed to indicate the stability of the devices, their potential to withstand low temperatures and the internal manufacturing integrity of the package. Although devices are not exposed to such extreme low temperatures in the field, the purpose of this test is to accelerate any failure mechanisms that could occur during long periods at storage temperatures.

Typical conditions:

$T_A = -65^{\circ}C$  on Plastic package Duration: 1000 hrs for qualification The test is performed by placing the devices in a mesh basket, then placed in a high temperature chamber at a controlled ambient temperature, as a function of time.

#### Steady State Operational Life (SSOL) Test

The SSOL test is designed to indicate the integrity of the chip and/or package assembly at steady-state continuous operational life conditions.

For IGBT's, parameters used to monitor performance are thermal resistance, threshold voltage, on-resistance, gate-emitter leakage current and collector-emitter leakage current.

Typical conditions:

$V_{GE} \geq 10~V$

$\Delta T_{\rm J} = 100^{\circ}{\rm C}$

$T_A = 25^{\circ}C$  Duration: 1000 hours for qualification.

A failure occurs when thermal fatigue causes the thermal resistance or the on-resistance to increase beyond the maximum value specified by the manufacturer's data sheet

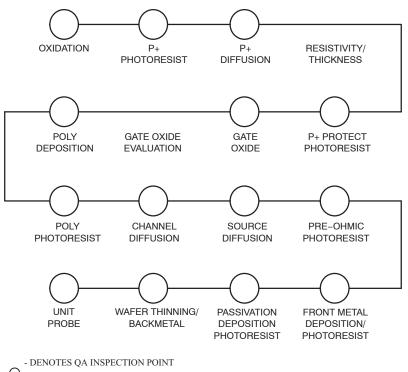

O - DENOTES PROCESS STEP

Figure 1. IGBT Wafer Fabrication

#### AND9058/D

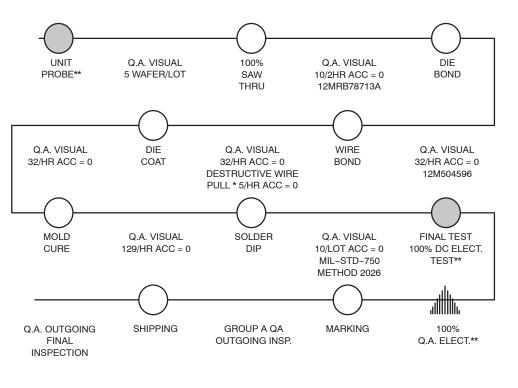

\*100% NON-DESTRUCTIVE WIRE PULL AFTER WIRE BOND \*\*100% DC ELECTRICAL TESTING

O – DENOTES PROCESS STEP

Figure 2. Assembly Process Flow

#### Environmental Package Related Test Programs:

- A.. Physical Dimensions This test is performed to determine the conformance to device outline drawing specifications.

- B. Visual and mechanical examination A test to determine the acceptability of product to certain cosmetic and functional criteria such as marking legibility, stains, etc.

- C.. Resistance to Solvents A test to determine the solderability of device terminals.

- D.. Terminal Strength This test is a lead bend test to check for lead strength.

Every manufacturing process exhibits a quality and reliability distribution. This distribution must be controlled to assure a high mean value, a narrow range and a consistent shape. Through proper design and process control this can be accomplished, thereby reducing the task of screening programs which attempt to eliminate the lower tail of the distribution.

#### **Accelerated Stress Testing**

The nature of some tests in this report is such that they far exceed that which the devices would see in normal operating conditions. Thus, the test conditions "accelerate" the failure mechanisms in question and allow ON Semiconductor to predict failure rates in a much shorter amount of time than otherwise possible. Failure modes that are temperature dependent are characterized by the Arrhenius model.

$$\mathsf{AF} = \frac{\mathsf{EA}}{\mathsf{K}} \Bigl( \frac{1}{\mathsf{T2}} - \frac{1}{\mathsf{T1}} \Bigr)$$

- DENOTES QA INSPECTION POINT

AF = Acceleration Factor

EA = Activation Energy (eV)

K = Boltzman's Constant (8.62 x 10E-5 eV/K)

T2 = Operating Temperature, K

T1 = Test Temperature, K

Therefore, the equivalent device hours are equal to the acceleration factor (as determined by the Arrhenius Model) times the actual device hours.

#### **Review of Data**

High Temperature Reverse Bias (HTRB) indicates the stability of leakage current, which is related to the field distortion of IGBT's. HTRB enhances the failure mechanism by high temperature reverse bias testing, and therefore is a good indicator of device quality and reliability, along with verification that process controls are effective.

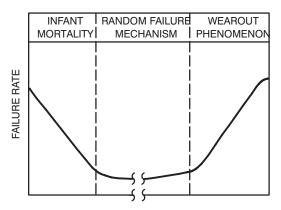

High Temperature Gate Bias (HTGB) checks the stability of the device under "gate bias" forward conditions at accelerated high temperature, as a function of time. This test is performed to electrically stress the gate oxide to detect for drift caused by random oxide defect. This failure mechanism appears in the infant and random zones of the reliability "bath tub curve" at a very low rate of defect.

Intermittent Operating Life (IOL) is an excellent accelerated stress test to determine the integrity of the chip

and/or package assembly to cycling on (device thermally heated due to power dissipation) and cycling off (device thermally cooling due to removal of power applied). This test is perhaps the most important test of all, along with simulating what is normally experienced in a "real world" environment. IOL exercises die bond, wire bonds, turning on the device, turning off the device, relates the device performance, and verifying the thermal expansion of all materials are compatible. ON Semiconductor performs extensive IOL testing as a continual process control monitor that test relates to the "device system\*\*" as a whole. ON Semiconductor also performs extensive analysis and comparison of delta function temperatures. ON Semiconductor has determined that to effectively stress the device a delta T<sub>J</sub> of 100°C is necessary which far exceeds many customers' application and determines the reliability modeling of the device.

Temperature Cycling (TC) is also an excellent stress test to determine the resistance of the device to high and low temperature excursions in an air medium. Where IOL electrically stresses the "device system" from internally, temperature cycle stresses the "device system" thermally from external environment conditions.

High Temperature Storage Life (HTSL), High Humidity Temperature Reverse Bias (H<sup>3</sup>TRB), Thermal Shock (TC) and "Pressure Cooker" (Autoclave) are routinely tested, however it is felt by ON Semiconductor Reliability Engineering that HTRB, HTGB, IOL and TC are of primary importance. ON Semiconductor has been in the semiconductor industry for many years and will remain there as a leader with continued reliability, quality and customer relations.

#### **RELIABILITY AUDIT PROGRAM**

At ON Semiconductor reliability is assured through the rigid implementation of a reliability audit program. All IGBT products are grouped into generic families according to process technology and package types. These families are sampled quarterly from the raw stock at final test, then submitted for audit testing. The extreme stress testing, in real-time for each product run, may uncover process abnormalities that are detectable by the in-process controls. Typical reliability audit tests include high temperature reverse bias, high temperature gate bias, intermittent operating life, temperature cycling, and autoclave. To uncover any hidden failure modes, the reliability tests are designed to exceed the testing conditions of normal quality and reliability testing.

Audit failures which are detected are sent to the product analysis laboratory for real-time evaluations. This highly specialized area is equipped with a variety of analytical capabilities, including electrical characterizations, wet chemical and plasma techniques, metallurgical cross-sectioning, scanning electron microscope, dispersive x-ray, auger spectroscopy, and micro/macro photography. Together, these capabilities allow the prompt and accurate analysis of failure mechanisms – ensuring that the results of the evaluations can be translated into corrective actions and directed to the appropriate areas of responsibility.

The ON Semiconductor reliability audit program provides a powerful method for uncovering even the slightest hint of potential process anomalies in the IGBT product line. It is this stringent and continuing concern with the reliability audits that gives positive assurance that customer satisfaction will be achieved.

| Test                 | Conditions                                                                                                                                                                                                                     | S/S   | Frequency |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------|

| HTRB                 | $\label{eq:VcE} \begin{array}{l} V_{CE} = 80 - 100\% \mbox{ Max} \\ Rating \\ V_{GE} = 0 \mbox{ V} \\ T_J = 150^{\circ} \mbox{C} \\ Duration = 168 \mbox{ Hours} \\ (short), \\ 1000 \mbox{ Hours} \mbox{ (long)} \end{array}$ | 77pcs | Qty       |

| HTGB                 | $\label{eq:VGES} \begin{array}{l} V_{GES} = \pm 20 \ V \\ V_{CE} = 0 \ V \\ T_J = 150^\circ C \\ Duration = 168 \ Hours \\ (short), \\ 1000 \ Hours \ (long) \end{array}$                                                      | 77pcs | Qty       |

| IOL                  | $\begin{array}{l} D \ T_J = 100^{\circ}C \\ V_{CE} \geq 10 \ V \\ Duration = 5000 \ Cycles \\ (short), \ 15,000 \ cycles \\ (long) \end{array}$                                                                                | 77pcs | Qty       |

| Solder Heat          | 1 Cycle @ 260°C for<br>10 seconds followed by:                                                                                                                                                                                 | 77pcs | Qty       |

| Temperature<br>Cycle | 100 Cycles (short)<br>500 Cycles (long)<br>-65 to +150°C<br>Dwell Time ≥ 15 minutes                                                                                                                                            | 77pcs | Qty       |

| Pressure<br>Cooker   | P = 15 psi, T = 121°C<br>Duration = 48 Hours<br>(short),<br>96 Hours (long)<br>(Plastic Package Only)                                                                                                                          | 77pcs | Qty       |

| HTSL                 | T <sub>A</sub> = 150°C, 168 hrs                                                                                                                                                                                                | 77pc  | Qty       |

#### IGBT RELIABILITY AUDIT PROGRAM

#### **Essentials of Reliability:**

Paramount in the mind of every semiconductor user is the question of device performance versus time. After the applicability of a particular device has been established, its effectiveness depends on the length of trouble free service it can offer. The reliability of a device is exactly that – an expression of how well it will serve the customer. Reliability can be redefined as the probability of failure free performance, under a given manufacturer's specifications, for a given period of time. The failure rate of semiconductors in general, when plotted versus a long period of time, exhibit what has been called the "bath tub curve".

Figure 3. Failure Rate of Semiconductor

#### **Reliability Mechanics**

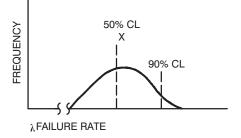

Since reliability evaluations usually involve only samples of an entire population of devices, the concept of the central limit theorem applies and a failure rate is calculated using the  $\lambda^2$  distribution through the equation:

$$\lambda 3 \frac{\lambda 2(\alpha, 2r + 2)}{2nt}$$

where

$$\alpha = \frac{100 - cl}{100}$$

The confidence limit is the degree of conservatism desired in the calculation. The central limit theorem states that the values of any sample of units out of a large population will produce a normal distribution. A 50% confidence limit is termed the best estimate, and is the mean of this distribution. A 90% confidence limit is a very conservative value and results in a higher  $\lambda$  which represents the point at which 90% of the area of the distribution is to the left of that value.

The term (2r + 2) is called the degrees of freedom and is an expression of the number of rejects in a form suitable to  $\lambda^2$  tables. The number of rejects is a critical factor since the definition of rejects often differs between manufacturers. Due to the increasing chance of a test not being representative of the entire population as sample size and

Figure 4. Confidence Limits and the Distribution of Sample Failure Rates

test time are decreased, the  $\lambda^2$  calculation produces surprisingly high values of  $\lambda$  for short test durations even though the true long term failure rate may be quite low. For this reason relatively large amounts of data must be gathered to demonstrate the real long term failure rate. Since this would require years of testing on thousands of devices, methods of accelerated testing have been developed.

Years of semiconductor device testing has shown that temperature will accelerate failures and that this behavior fits the form of the Arrhenius equation:

$$R(t) = Ro(t)e^{-/KT}$$

Where R(t) = reaction rate as a function of time and temperature

$R_o = A constant$

t = Time

T = Absolute temperature, °Kelvin (°C + 273°)

= Activation energy in electron volts (ev)

K = Boltzman's constant =  $8.62 \times 10^{-5} \text{ ev}/^{\circ}\text{K}$

This equation can also be put in the form:

AF = Acceleration factor

- T2 = User temperature

- T1 = Actual test temperature

The Arrhenius equation states that reaction rate increases exponentially with the temperature. This produces a straight line when plotted on log–linear paper with a slope physically interpreted as the energy threshold of a particular reaction or failure mechanism.

#### **Reliability Qualifications/Evaluations Outline:**

Some of the functions of ON Semiconductor Reliability and Quality Assurance Engineering is to evaluate new products for introduction, process changes (whether minor or major), and product line updates to verify the integrity and reliability of conformance, thereby ensuring satisfactory performance in the field. The reliability evaluations may be subjected to a series of extensive reliability testing, such as those outlined in the "Tests Performed" section, or special tests, depending on the nature of the qualification requirement.

# AND9068/D

# Reading ON Semiconductor IGBT Datasheets

#### **ON Semiconductor®**

http://onsemi.com

### **APPLICATION NOTE**

#### Table 1. ABSOLUTE MAXIMUM RATINGS

| Rating                                                                                  | Symbol           | Value          | Unit |

|-----------------------------------------------------------------------------------------|------------------|----------------|------|

| Collector-emitter voltage                                                               | V <sub>CES</sub> | 600            | V    |

| Collector current<br>@ Tc = 25°C<br>@ Tc = 100°C                                        | Ι <sub>c</sub>   | 30<br>15       | A    |

| Pulsed collector current,<br>T <sub>pulse</sub> limited by T <sub>Jmax</sub>            | I <sub>CM</sub>  | 60             | A    |

| Diode forward current<br>@ Tc = 25°C<br>@ Tc = 100°C                                    | Ι <sub>F</sub>   | 30<br>15       | A    |

| Diode pulsed current, T <sub>pulse</sub><br>limited by T <sub>Jmax</sub>                | I <sub>FM</sub>  | 60             | A    |

| Gate-emitter voltage                                                                    | V <sub>GE</sub>  | ±20            | V    |

| Power dissipation<br>@ Tc = 25°C<br>@ Tc = 100°C                                        | P <sub>D</sub>   | 130<br>55      | W    |

| Short circuit withstand time $V_{GE}$ = 15 V, $V_{CE}$ = 400 V, $T_J \le +150^{\circ}C$ | t <sub>SC</sub>  | 10             | μs   |

| Operating junction temperat-<br>ure range                                               | TJ               | –55 to<br>+150 | °C   |

| Storage temperature range                                                               | T <sub>stg</sub> | –55 to<br>+150 | °C   |

| Lead temperature for solder-<br>ing, 1/8" from case for<br>5 seconds                    | T <sub>SLD</sub> | 260            | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Absolute Maximum Ratings

The absolute maximum ratings shown in Table 1 are typical for an IGBT. This table sets the limits, both electrical

#### Abstract

The Insulated Gate Bipolar Transistor is a power switch well suited for high power applications such as motor control, UPS and solar inverters, and induction heating. If the application requirements are well understood, the correct IGBT can easily be selected from the electrical properties provided in the manufacturers' datasheet. This application note describes the electrical parameters provided in the ON Semiconductor IGBT datasheet.

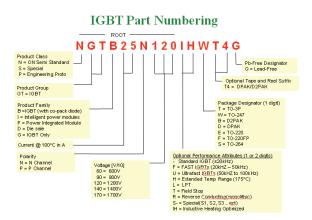

#### Part Number

The part numbering convention for ON Semiconductor IGBTs is shown in Figure 1. Many of the device ratings and details are described in the part number and can be understood using this code.

Figure 1. ON Semiconductor IGBT Part Numbering Key

#### Brief

This section provides a description of the device and lists its key features and typical applications.

and thermal, beyond which the functionality is no longer guaranteed and at which physical damage may occur. The absolute maximum rating does not guarantee that the device will meet the data sheet specifications when it is within that range. The specific voltage, temperature, current and other limitations are called out in the Electrical Characteristics table.

#### Collector-Emitter Voltage, V<sub>CES</sub>

The maximum rated voltage to be applied between the collector and emitter terminals of the device is specified to prevent the device from entering avalanche breakdown and dissipating excessive energy in the device. The avalanche breakdown voltage varies with temperature and is at its minimum at low temperature. The breakdown voltage of the device is designed to meet the minimum voltage rating at  $-40^{\circ}$ C.

#### Collector Current, I<sub>C</sub>

The maximum collector current is defined as the amount of current that is allowed to flow continuously into the collector for a given case temperature,  $T_C$ , in order to reach the maximum allowable junction temperature,  $T_J$  (150°C). The collector current can be stated in the following equation form:

$$I_{C} = \frac{T_{J} - T_{C}}{R_{th(j-c)(IGBT)} \cdot V_{CE(sat)}}$$

where  $R_{th(j-c)}$  is the thermal resistance of the package and  $V_{CE(sat)}$  is the on–state voltage at the specified current, I<sub>C</sub>. Since it is the current being sought after, and  $V_{CE(sat)}$  is a function of current, the equation must be solved iteratively. An estimate of the  $V_{CE(sat)}$  for a given collector current and temperature can found in the typical datasheet curves, discussed later.

It is very important to understand that the absolute maximum collector current is defined based on very specific electrical and thermal conditions. The capability of the IGBT to conduct current without exceeding the absolute maximum junction temperature is highly dependent on the thermal performance of the system, including heatsinks and airflow.

#### Pulsed Collector Current, ICM

The pulsed collector current describes the peak collector current pulse above the rated collector current specification that can flow while remaining below the maximum junction temperature. The maximum allowable pulsed current in turn depends on the pulse width, duty cycle and thermal conditions of the device.

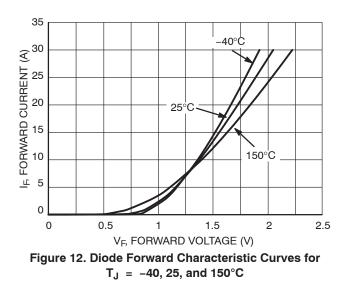

#### Diode Forward Current, IF

The diode forward current is the maximum continuous current that can flow at a fixed case temperature,  $T_C$ , while remaining under the maximum junction temperature,  $T_J$ . This is determined in similar fashion to the  $V_{CE(sat)}$ , above.

$$\mathsf{I}_\mathsf{F} = \frac{\mathsf{T}_\mathsf{J} - \mathsf{T}_\mathsf{C}}{\mathsf{R}_{\mathsf{th}(j-c)(\mathsf{diode})} \cdot \mathsf{V}_\mathsf{F}}$$

The equation relating  $I_F$  and  $V_F$  to the temperature rise is the same, although the  $R_{th(j-c)}$  for the diode is specified separately.

#### Diode Pulsed Current, I<sub>FM</sub>

The pulsed diode current describes the peak diode current pulse above the rated collector current specification that can flow while the junction remains below its maximum temperature. The maximum allowable pulsed current in turn depends on the pulse width, duty cycle and thermal conditions of the device.

#### Gate-Emitter Voltage, VGE

The gate–emitter voltage,  $V_{GE}$  describes maximum voltage to be applied from gate to emitter under fault conditions. The gate–emitter voltage is limited by the gate oxide material properties and thickness. The oxide is typically capable of withstanding greater than 80V before the oxide ruptures, but to ensure reliability over the lifetime of the device, and to allow for transient overvoltage conditions in the application, this voltage is limited to well below the gate rupture voltage.

#### Power Dissipation, PD

The maximum power dissipation is determined using the following equation:

$$P_{D} = \frac{T_{J} - T_{C}}{R_{th(j-c)}}$$

where  $R_{th(j-c)}$  is the thermal resistance of the package. The maximum power dissipation is given at case temperatures of 25°C and 100°C, where the maximum junction temperature is 150°C.

#### Short Circuit Withstand Time, tsc

The short circuit withstand time describes the ability of the device to carry high current and sustain high voltage at the same time. The device must withstand at least the rated short circuit withstand time with specified voltages applied from collector to emitter and from gate to emitter. The collector–emitter voltage specified for the test will vary based on the minimum blocking voltage capability of the device. The gate–emitter voltage is usually 15 V. The current flowing through the device under these conditions can far exceed the rated current, and is limited by the IGBT forward transconductance, an electrical parameter described below. The failure mode during this fault condition is usually thermal in nature.

#### **Operating Junction Temperature Range, T<sub>J</sub>**

This is the junction temperature range in which the device is guaranteed to operate without physical or electrical damage or reduced life expectancy.

#### Storage Temperature Range, T<sub>stg</sub>

This is the temperature range in which the device may be stored, without electrical bias, without reducing the life expectancy of the device.

#### Lead Temperature for Soldering, T<sub>SLD</sub>

The maximum allowable soldering temperature is limited by the thermal conduction from the leads to the junction and

#### THERMAL CHARACTERISTICS

die attach regions of the device. The maximum lead temperature is also dependent on the duration for which the soldering iron is applied to the lead. The maximum time for application of the heat is specified in the conditions of this rating.

#### Table 2. TABLE OF IGBT AND DIODE THERMAL CHARACTERISTICS

| Rating                                         | Symbol               | Value | Unit |

|------------------------------------------------|----------------------|-------|------|

| Thermal resistance junction to case, for IGBT  | R <sub>th(j-c)</sub> | 1.1   | °C/W |

| Thermal resistance junction to case, for Diode | R <sub>th(j-c)</sub> | 2.4   | °C/W |

| Thermal resistance junction to ambient         | R <sub>th(j-a)</sub> | 60    | °C/W |

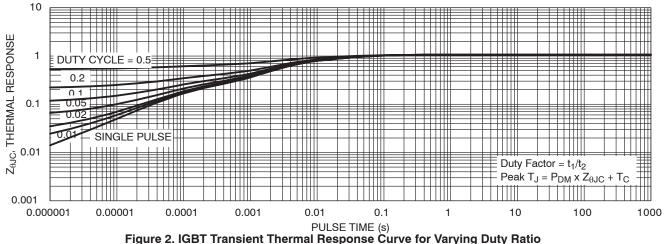

#### Thermal Resistance Junction-to-Case, Rth(i-c)

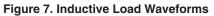

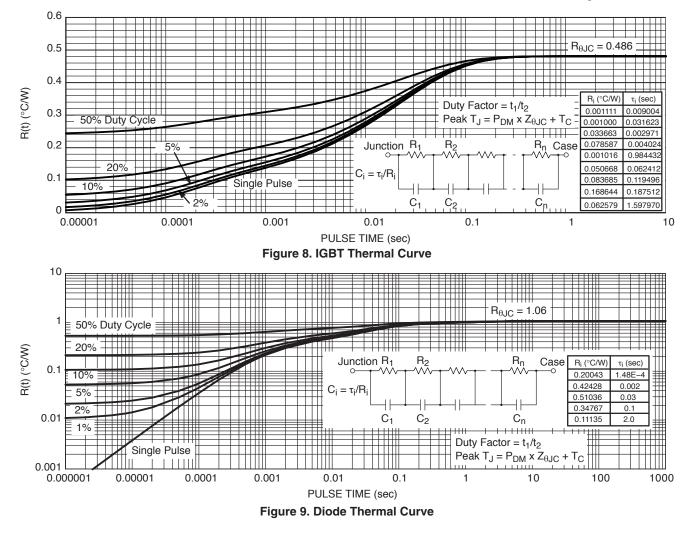

The value for the thermal resistance given in Table 2 represents the steady-state thermal resistance under dc power conditions, applied to the IGBT. The thermal

resistance is derated for a square power pulse for reference in designing pulse width modulated applications and is described in the graph of thermal resistance for varying pulse width and duty ratio, shown in Figure 2, below.

For a copackaged device such as the NGTB15N60EG the thermal resistance from the junction to case is specified separately for the IGBT and the diode.

#### Thermal Resistance Junction-to-Ambient, R<sub>th(i-a)</sub>

This is the entire thermal resistance from the silicon junction-to-ambient.

#### **Electrical Characteristics**

#### Static Characteristics

The static, or dc, electrical characteristics are shown in Table 3.

| Parameter                                                         | Test Conditions                                                        | Symbol               | Min | Тур        | Max         | Unit |

|-------------------------------------------------------------------|------------------------------------------------------------------------|----------------------|-----|------------|-------------|------|

| STATIC CHARACTERISTIC                                             |                                                                        |                      |     |            |             |      |

| Collector-emitter breakdown voltage, gate-emitter short-circuited | $V_{GE}$ = 0 V, I <sub>C</sub> = 500 µA                                | V <sub>(BR)CES</sub> | 600 | -          | -           | V    |

| Collector-emitter saturation voltage                              | $V_{GE}$ = 15 V , I_C = 15 A $V_{GE}$ = 15 V , I_C = 15 A, T_J = 150°C | V <sub>CEsat</sub>   | -   | 1.7<br>2.1 | 1.95<br>2.4 | V    |

| Gate-emitter threshold voltage                                    | $V_{GE}$ = $V_{CE}$ , $I_C$ = 250 $\mu$ A                              | V <sub>GE(th)</sub>  | 4.5 |            | 6.5         | V    |

Page 19

#### Table 3. IGBT STATIC ELECTRICAL CHARACTERISTICS

| Parameter                                                       | Test Conditions                                                                       | Symbol           | Min | Тур     | Max      | Unit |

|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|------------------|-----|---------|----------|------|

| STATIC CHARACTERISTIC                                           |                                                                                       |                  |     |         |          |      |

| Collector-emitter cut-off current, gate-emitter short-circuited | $V_{GE}$ = 0 V, $V_{CE}$ = 600 V<br>$V_{GE}$ = 0 V, $V_{CE}$ = 600 V, $T_{J}$ = 150°C | I <sub>CES</sub> |     | 10<br>- | _<br>200 | μΑ   |

| Gate leakage current, collector-emitter<br>short-circuited      | $V_{GE}$ = 20 V, $V_{CE}$ = 0 V                                                       | I <sub>GES</sub> | -   | -       | 100      | nA   |

| Forward Transconductance                                        | $V_{CE} = 20 \text{ V}, \text{ I}_{C} = 15 \text{ A}$                                 | 9 <sub>fs</sub>  | -   | 10.1    | -        | S    |

#### Collector-Emitter Breakdown Voltage, V(BR)CES

This is the minimum off-state forward blocking voltage guaranteed over the operating temperature range. It is specified with the gate terminal tied to the emitter with a specified collector current large enough to place the device into avalanche.

#### Collector-Emitter Saturation Voltage, V<sub>CE(sat)</sub>

$V_{CE(sat)}$  is an important figure of merit, since it is directly related to the conduction losses of the device. This is the voltage drop from collector to emitter for a specified gate voltage and collector current. Both a typical value and a maximum value are specified in the electrical table for both 25°C and 150°C.

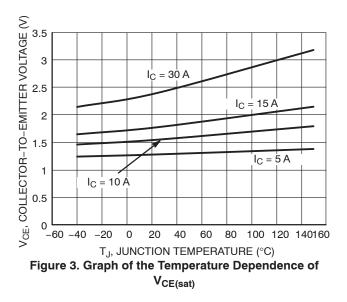

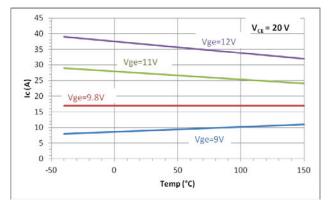

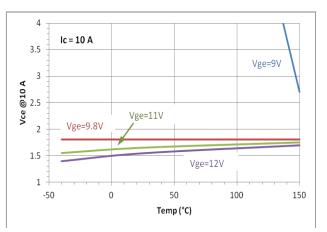

In addition to the electrical limits in the table, the datasheet includes a graph describing the dependence of  $V_{CE(sat)}$  on temperature, as shown in Figure 3. The graph describes the typical part and does not guarantee performance, but it can be used as a starting point to determine the  $V_{CE(sat)}$  for a given temperature. The curves are given for  $V_{GE} = 15$  V and various collector currents.

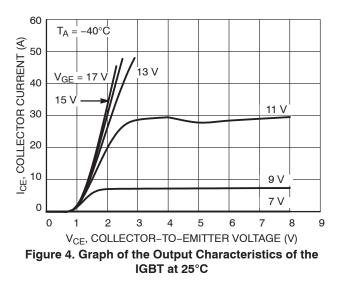

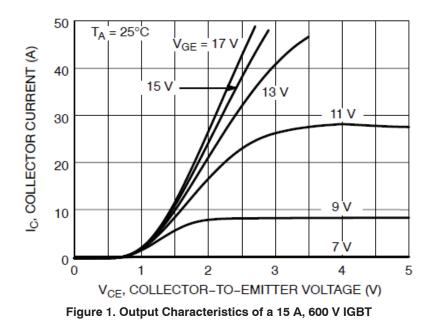

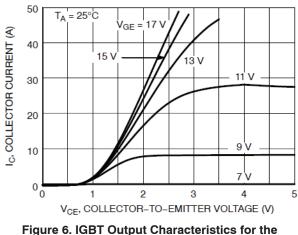

The  $V_{CE(sat)}$  values in the electrical parameter table are only given for  $V_{GE} = 15$  V. If the gate of the IGBT is being driven by a different voltage, the output characteristics shown in Figure 4 can also be useful in approximating the  $V_{CE(sat)}$ . This chart shows the I<sub>C</sub> dependence on V<sub>CE</sub> for various gate–emitter voltages. The datasheet contains output characteristics for T<sub>A</sub> = -40, 25, and 150°C.

The characteristic curves and typical relationships should never be substituted for worst case design values. Good design practices and board–level design evaluation are critical for a reliable system.

#### Gate-Emitter Threshold Voltage, VGE(th)

This parameter describes the gate to emitter voltage required for a specified amount of collector current to flow. This defines the gate to emitter voltage at which the device enters the on–state. Typically this test is based on a collector current flow proportional to the die size.

#### Collector-Emitter Cut-off-Current, ICES

This specifies the leakage current one can expect in the off-state forward blocking mode. It is specified at the maximum rated blocking voltage,  $V_{CES}$  with the gate-to-emitter voltage equal to zero volts. The maximum allowable value of leakage current occurs at the maximum junction temperature.

#### Gate Leakage Current, IGES

The absolute maximum value of gate leakage current is typically specified at a gate voltage of 20 V while the collector and emitter are grounded.

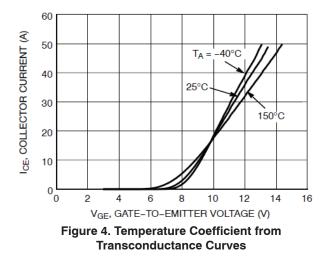

#### Forward Transconductance, g<sub>fs</sub>

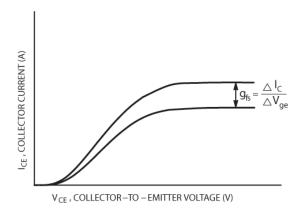

This is the amount of change in collector current for an incremental change in the gate to emitter voltage, measured in Siemens (or Mhos). It is specified at the room temperature rated current of the device, and typically with the device in full saturation, where a further increase in collector–emitter voltage no longer leads to an additional increase in collector current. A typical collector–emitter voltage used for this test is 20 V. Figure 5 illustrates the  $g_{fs}$  measurement.

Figure 5. Illustration of the Measurement of IGBT g<sub>fs</sub>

#### **Dynamic Characteristics**

#### **Table 4. IGBT Dynamic Electrical Characteristics**

| Parameter                    | Test Conditions                                                        | Symbol           | Min | Тур  | Max | Unit |

|------------------------------|------------------------------------------------------------------------|------------------|-----|------|-----|------|

| DYNAMIC CHARACTERISTIC       |                                                                        |                  |     |      |     |      |

| Input capacitance            |                                                                        | C <sub>ies</sub> | -   | 2600 | -   |      |

| Output capacitance           | V <sub>CE</sub> = 20 V, V <sub>GE</sub> = 0 V, f = 1 MHz               | C <sub>oes</sub> | -   | 64   | -   | pF   |

| Reverse transfer capacitance |                                                                        | C <sub>res</sub> | -   | 42   | -   |      |

| Gate charge total            |                                                                        | Qg               |     | 80   |     |      |

| Gate to emitter charge       | V <sub>CE</sub> = 480 V, I <sub>C</sub> = 15 A, V <sub>GE</sub> = 15 V | Q <sub>ge</sub>  |     | 24   |     | nC   |

| Gate to collector charge     |                                                                        | Q <sub>gc</sub>  |     | 33   |     |      |

The dynamic electrical characteristics which include device capacitances and gate charge are given in the electrical table, as shown in Table 4.

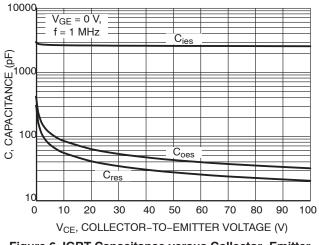

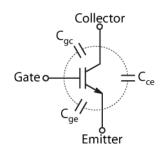

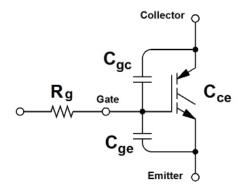

IGBT capacitances are similar to those described for power MOSFETs. The datasheet describes the measurable terminal capacitances,  $C_{ies}$ ,  $C_{oes}$ , and  $C_{res}$ . They are specified in the electrical table at a fixed collector bias voltage; however, the capacitances are voltage dependant, as can be seen in Figure 6. The capacitances specified on the datasheet are convenient and easily measured. They relate to the pin to pin capacitances shown in Figure 7 and described below.

Figure 6. IGBT Capacitance versus Collector–Emitter Voltage Showing Voltage Dependance of  $\rm C_{oes}$  and  $\rm C_{res}$

Figure 7. Pin-to-pin Capacitances of the IGBT

$$\begin{split} C_{ies} &= C_{ge} + C_{gc} \text{ with } C_{ce} \text{ shorted} \\ C_{oes} &= C_{gc} + C_{ce} \\ C_{res} &= C_{qc} \end{split}$$

#### Input Capacitance, Cies

The input capacitance is made up of the parallel combination of gate-emitter and gate-collector capacitances, when the collector and emitter are tied together. The gate-emitter capacitance is constant, as it consists mainly of the metal-oxide-semiconductor capacitance. The gate-collector capacitance is a combination of a fixed oxide capacitor and a p-n junction capacitor. This results in a voltage dependence that is slightly more complex than that of a p-n junction.

#### Output Capacitance, Coes

The output capacitance is formed by the parallel combination of the gate-collector and collector-emitter capacitances. As mentioned above, the gate-collector capacitance is voltage dependant. This is also true for the collector-emitter capacitance. The voltage dependence of the collector-emitter junction is that of a p-n junction.

#### Transfer Capacitance, Cres

The transfer capacitance is composed only of the gate–collector capacitance. Its role in the device operation is critical, as it provides negative feedback between the collector and the gate. This capacitance is responsible for the plateau on the gate charge curve. The change in collector–emitter voltage forces a current through  $C_{res}$  which reduces the gate drive current while the collector voltage is changing.

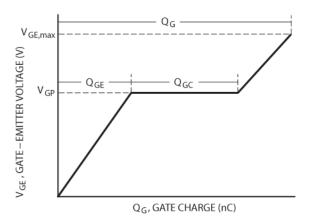

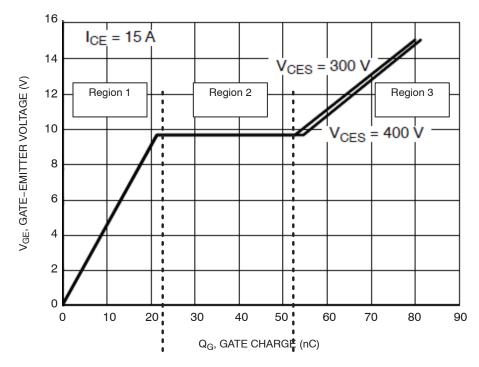

#### Gate Charge, Total, Qg

Input capacitance is useful, but in terms of gate drive design, the more important figure of merit is the gate charge. It is used to size the gate drive components and predict switching losses in the driver. To measure gate charge the IGBT gate is driven with a current and the gate voltage change is monitored versus time. The resulting gate voltage versus gate charge curve is shown in Figure 8 for a constant current gate drive signal.  $Q_g$  is the total charge required on the gate to raise  $V_{GE}$  to a specified gate voltage. ON Semiconductor devices are specified at  $V_{GE}$  = 15 V.

Figure 8. Theoretical Gate Charge Curve showing  $V_{GP},\,Q_G,\,Q_{GE},\,\text{and}\,\,Q_{GC}$

#### Gate to Emitter Charge, Qge

$Q_{ge}$  is the amount of charge required to reach the plateau voltage  $V_{GP}$ . This charge contributes to turning on the MOS channel, at which time the collector–emitter voltage begins to transition from high to low voltage. The level of  $V_{GP}$  is dependent on the load current being switched and can be approximated by determining the  $V_{GS}$  that corresponds to the switching current level from the transconductance curves in Figure 5.

#### Gate to Collector Charge, Q<sub>gc</sub>

$Q_{gc}$  is the amount of charge required to charge the junction capacitor while the voltage from collector to emitter is decreasing in the transition between the off-state and on-state. This plateau corresponds to the charging of what is also known as the Miller capacitance.

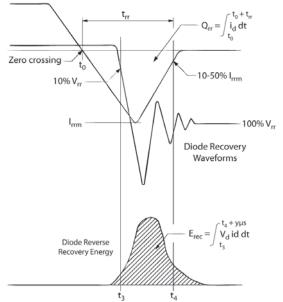

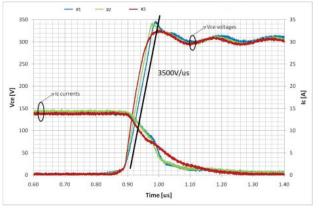

#### Switching Characteristics

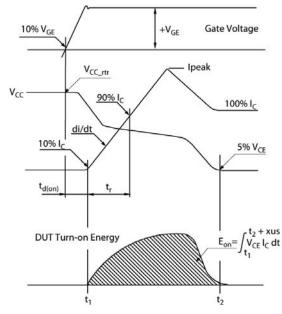

The IGBT switching characteristics are of great importance because they relate directly to the switching energy losses of the device. Switching losses can be substantial, especially at higher frequencies and increasing temperature, where the switching losses increase.

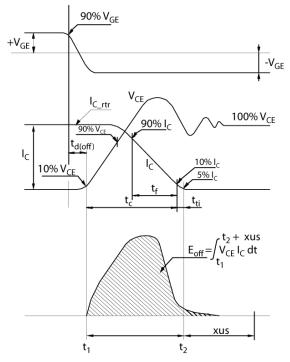

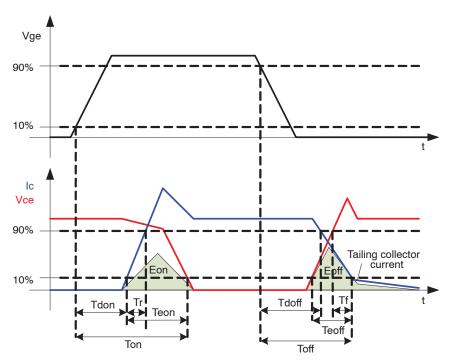

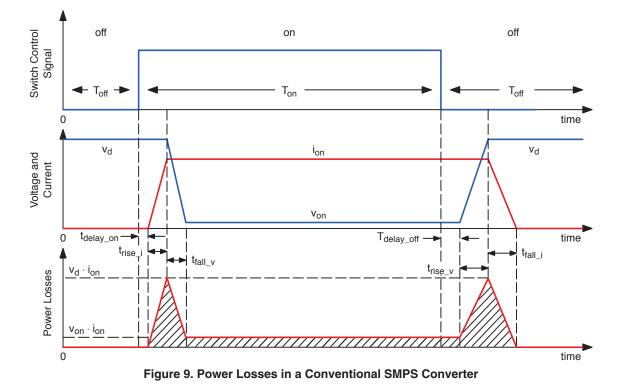

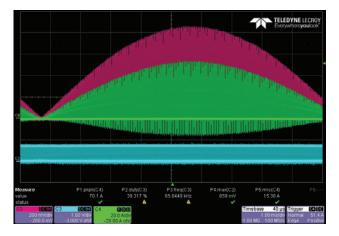

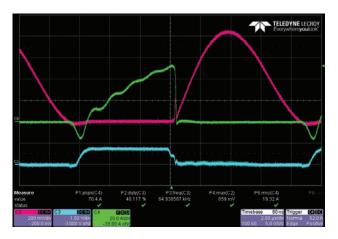

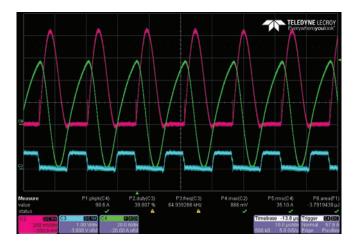

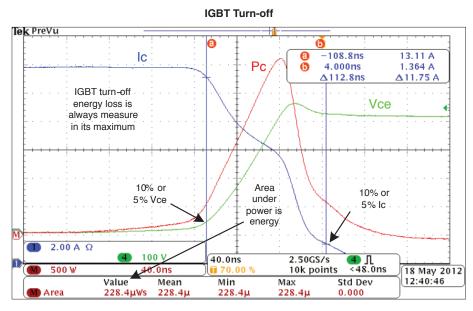

When voltage is applied to the gate, the input capacitance must first be charged to the threshold voltage,  $V_{GE(th)}$ . This leads to a delay ( $t_{d(on)}$ ) before the IGBT collector current begins to flow. Once the collector current begins to flow, the depletion layer that blocks the voltage during the off-state begins to collapse. The voltage drops to the on-state voltage drop,  $V_{CE(sat)}$ . This is illustrated in Figure 9.

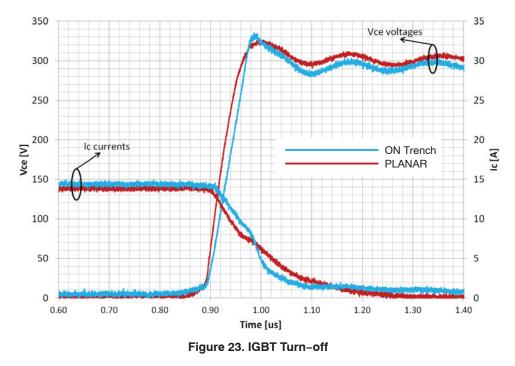

During turn-off, the gate voltage is reduced to zero and the opposite occurs. The channel for the MOSFET current is closed and the current begins to drop abruptly. The voltage

### AND9068/D

begins to rise from  $V_{CE(sat)}$  as the charge due to current flow is removed. The voltage across the device reaches the supply voltage, and minority carriers that remain in the device after turn-off cause a tail current that continues to flow. This is illustrated in Figure 10. The switching characteristics are given in the electrical parametric table for  $T_J = 25$  and 150°C. These are shown in Table 5.

| Parameter                                 | Test Conditions                                                                                                                            | Symbol              | Min | Тур   | Max | Unit |  |  |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-------|-----|------|--|--|

| SWITCHING CHARACTERISTIC , INDUCTIVE LOAD |                                                                                                                                            |                     |     |       |     |      |  |  |

| Turn-on delay time                        | $T_{J} = 25^{\circ}C$<br>$V_{CC} = 400 \text{ V, } I_{C} = 15 \text{ A}$<br>$R_{g} = 22 \Omega$<br>$V_{GE} = 0 \text{ V} / 15 \text{ V}$   | t <sub>d(on)</sub>  |     | 78    |     | ns   |  |  |

| Rise time                                 |                                                                                                                                            | t <sub>r</sub>      |     | 30    |     |      |  |  |

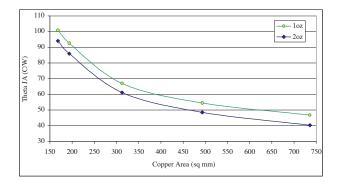

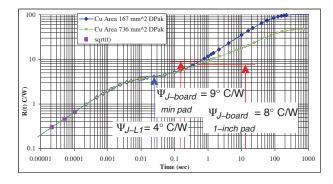

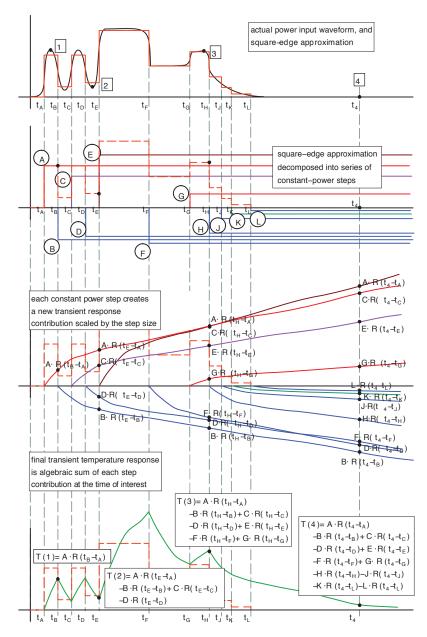

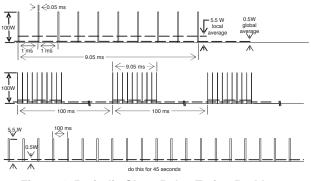

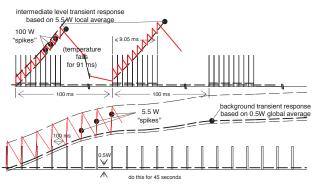

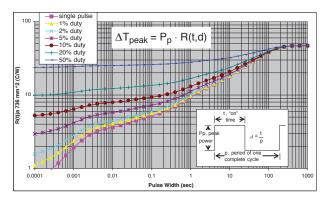

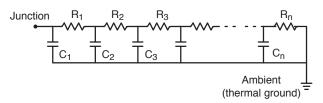

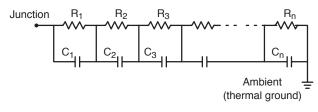

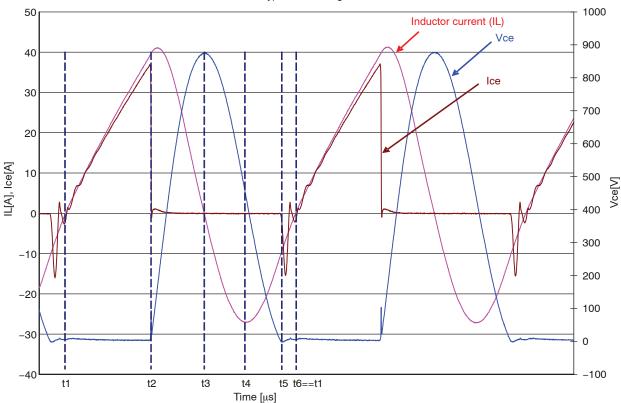

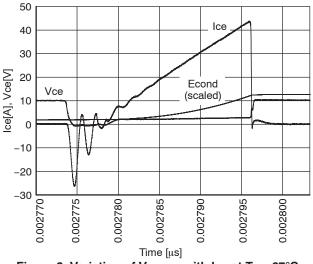

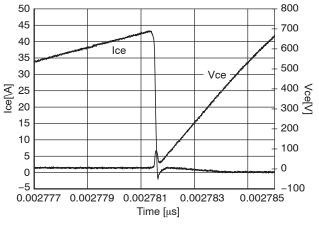

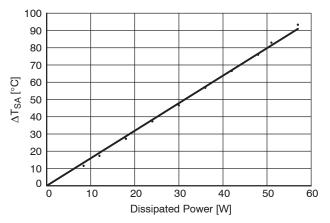

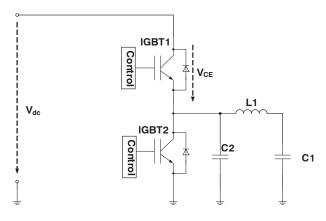

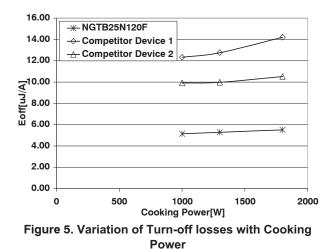

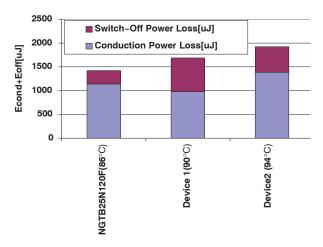

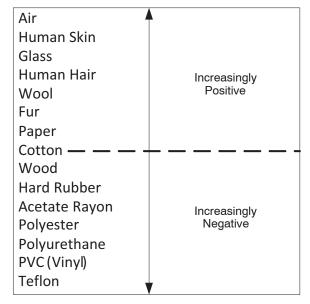

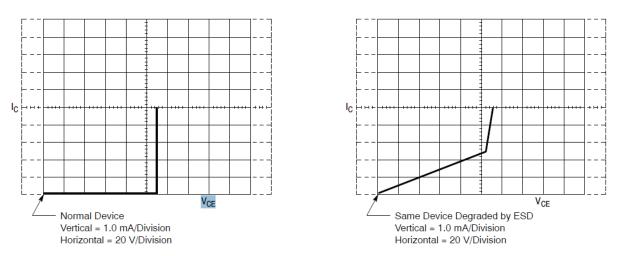

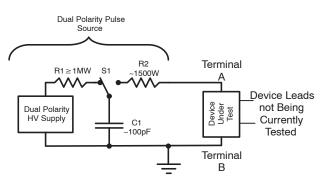

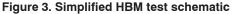

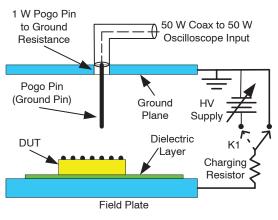

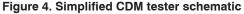

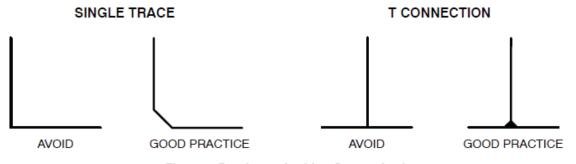

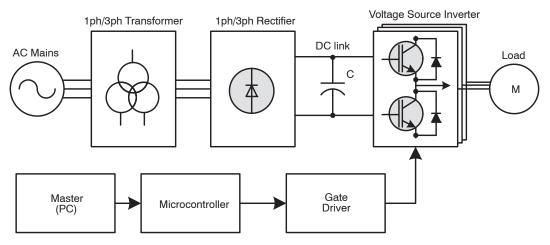

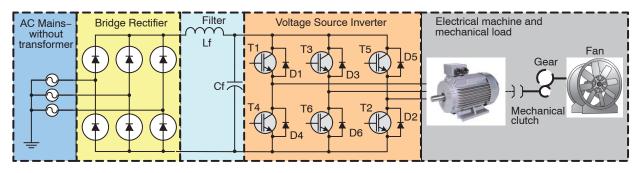

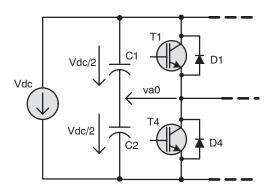

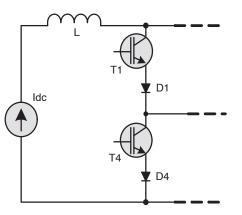

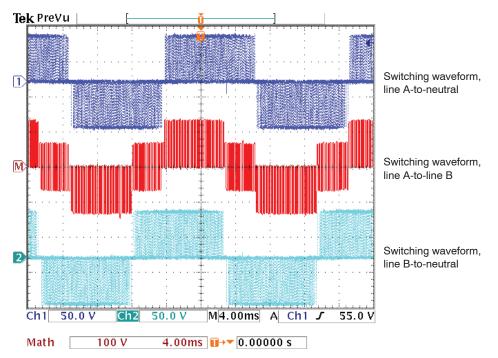

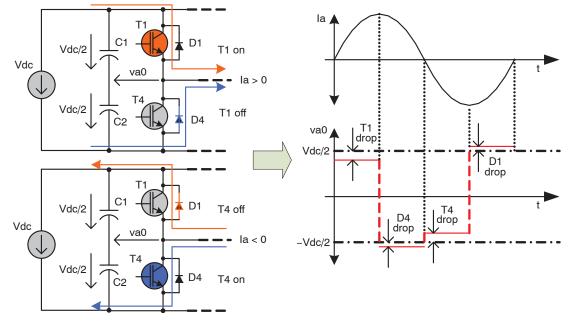

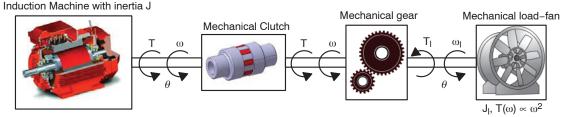

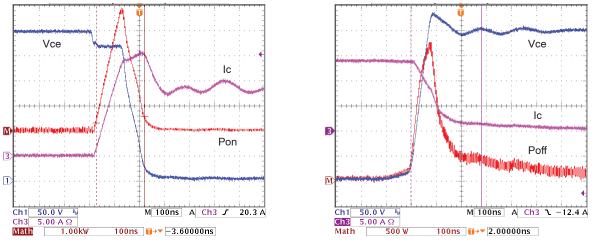

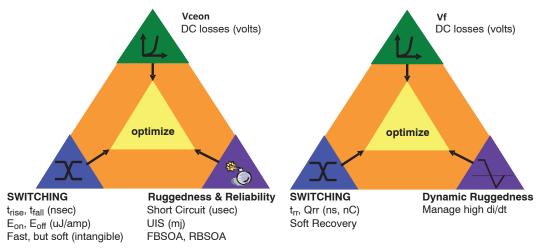

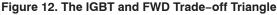

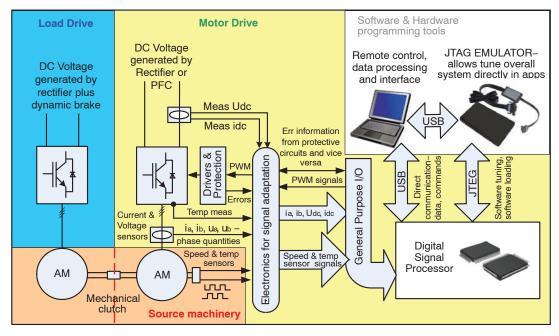

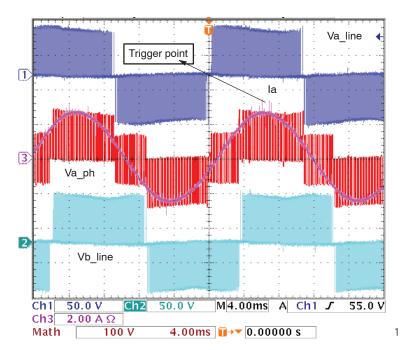

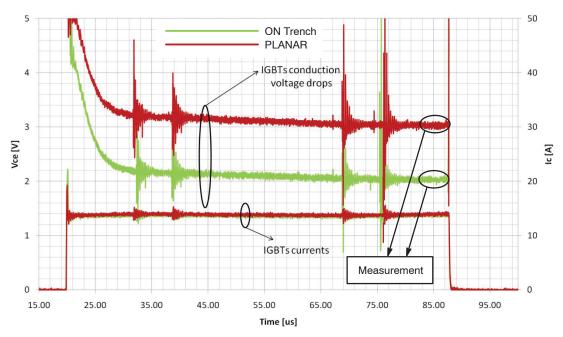

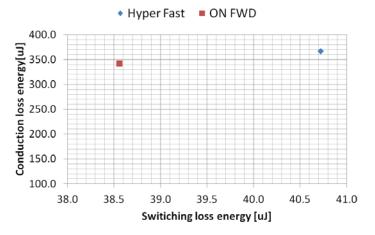

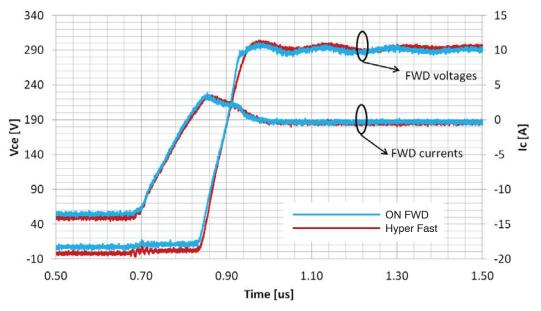

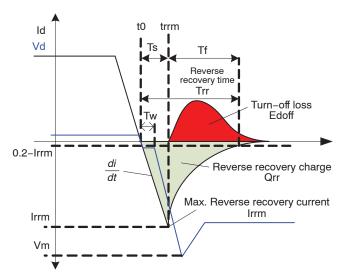

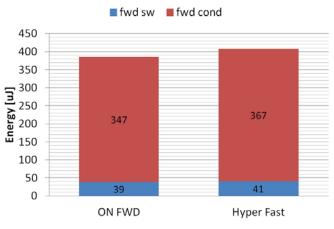

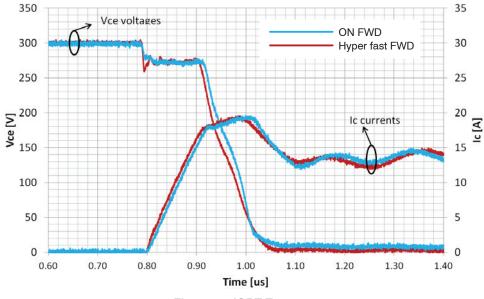

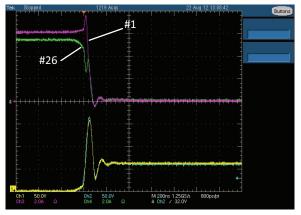

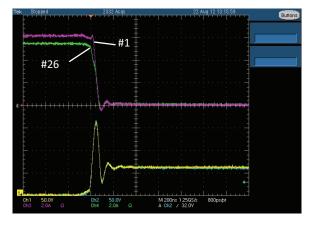

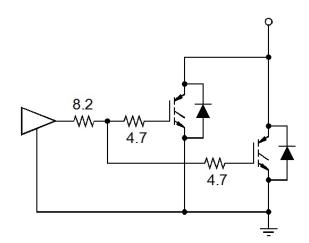

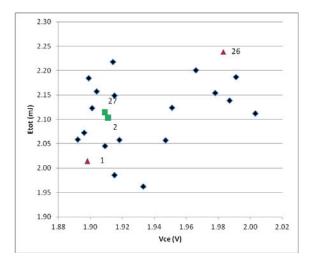

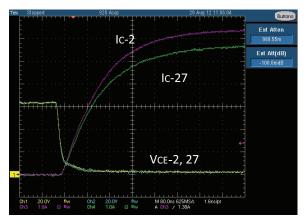

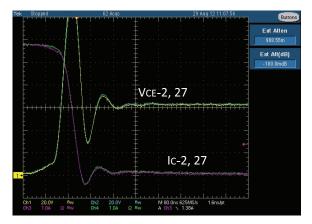

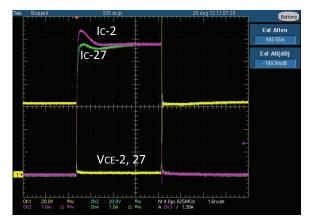

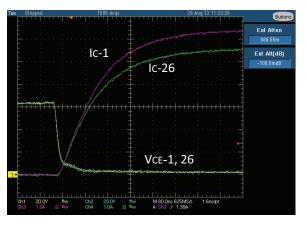

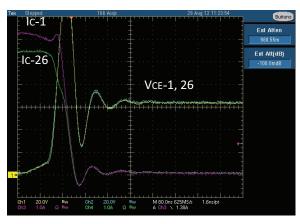

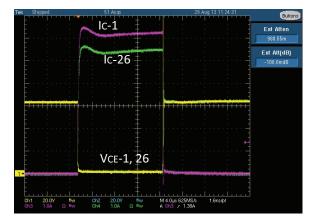

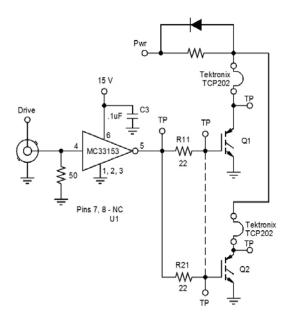

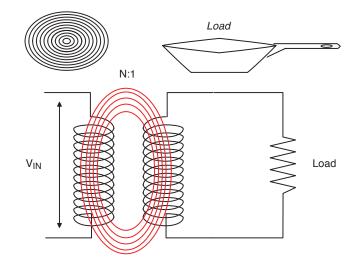

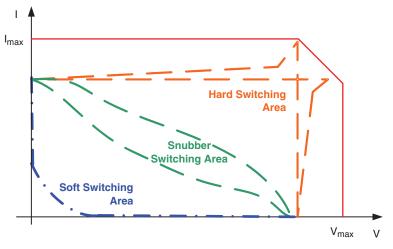

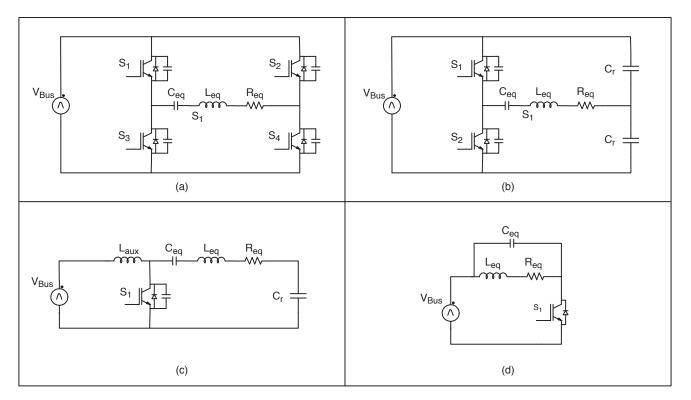

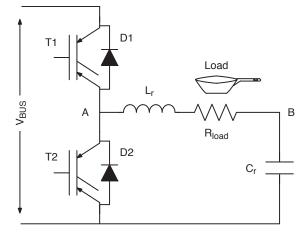

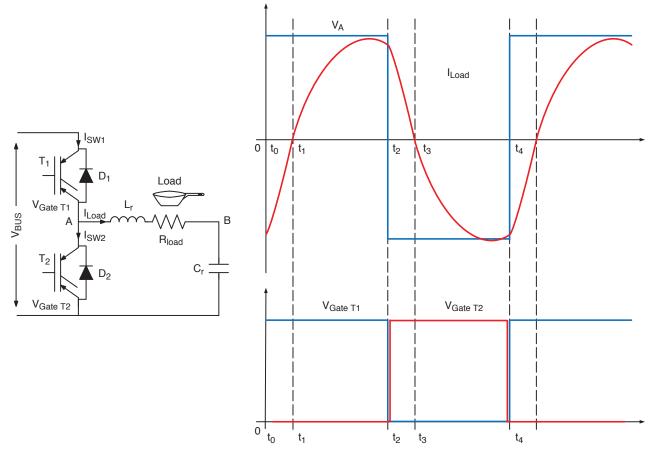

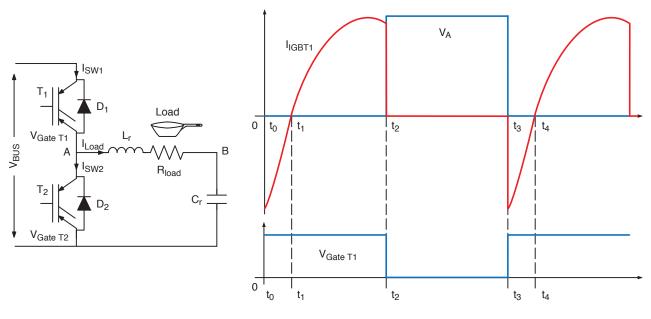

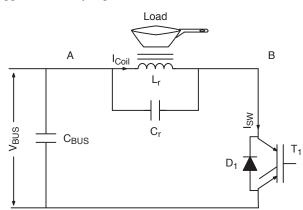

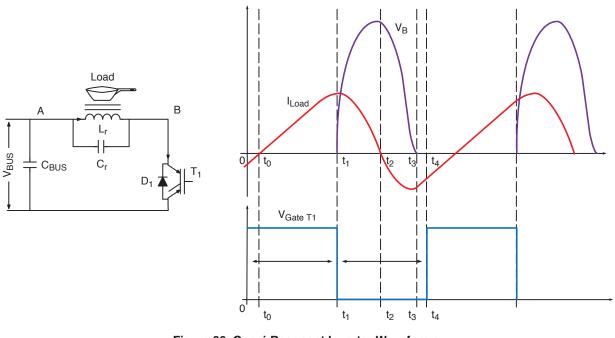

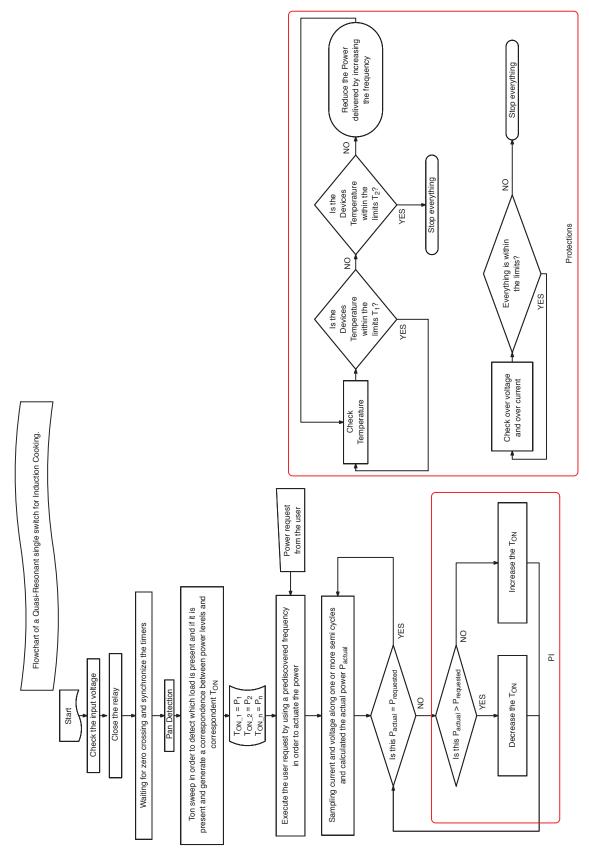

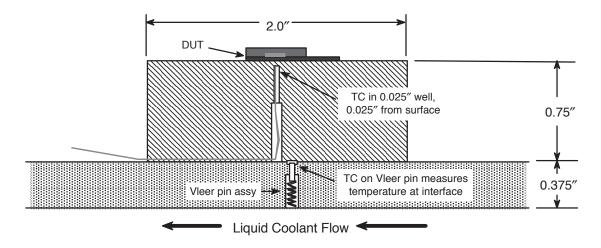

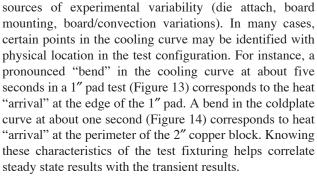

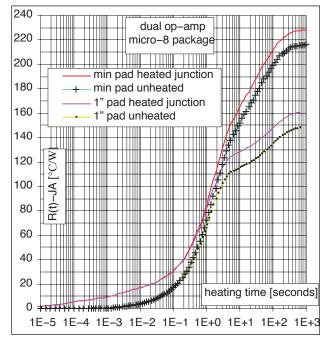

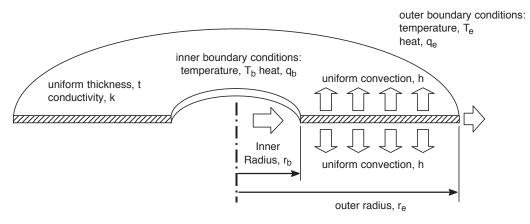

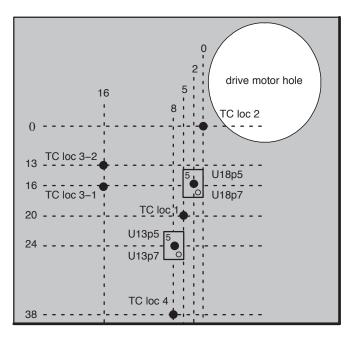

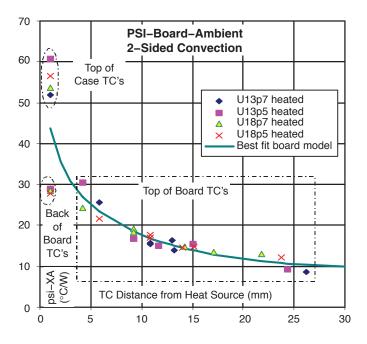

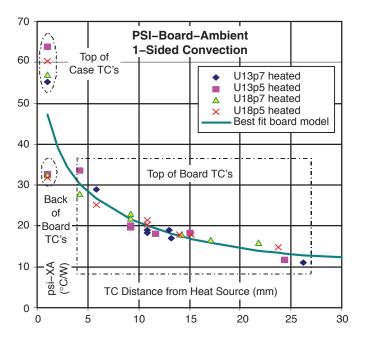

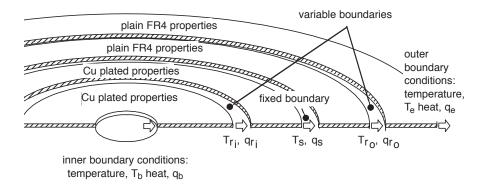

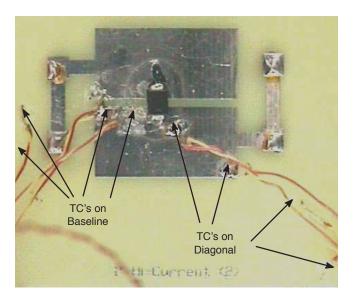

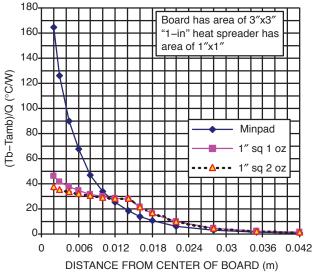

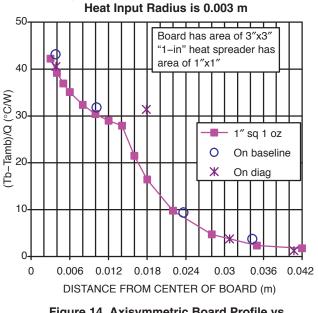

| Turn-off delay time                       |                                                                                                                                            | t <sub>d(off)</sub> |     | 130   |     |      |  |  |